STR-ZA1000ES/ZA2000ES/ZA3000ES

STR-ZA1000ES/ZA2000ES/ZA3000ES

4646

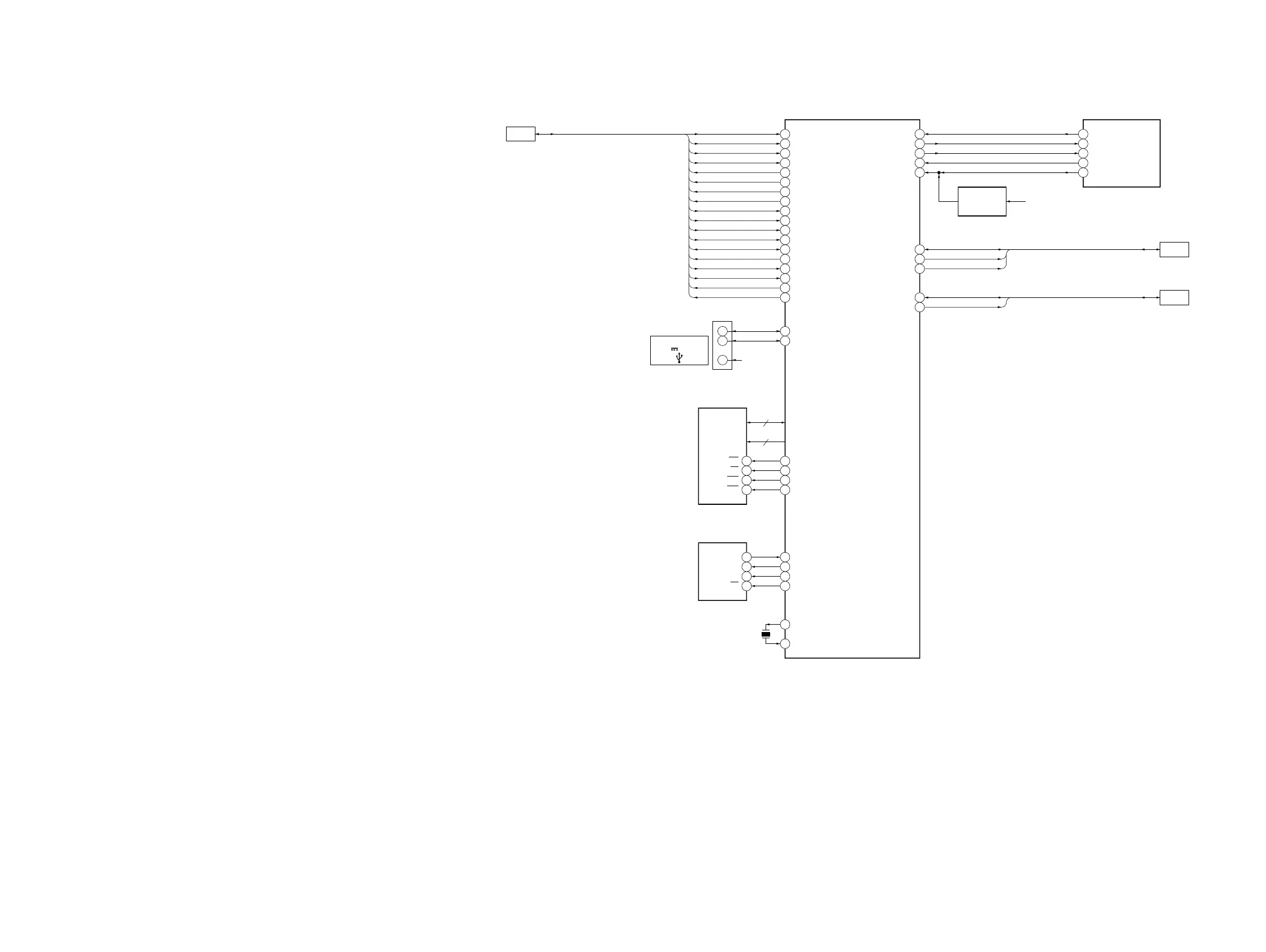

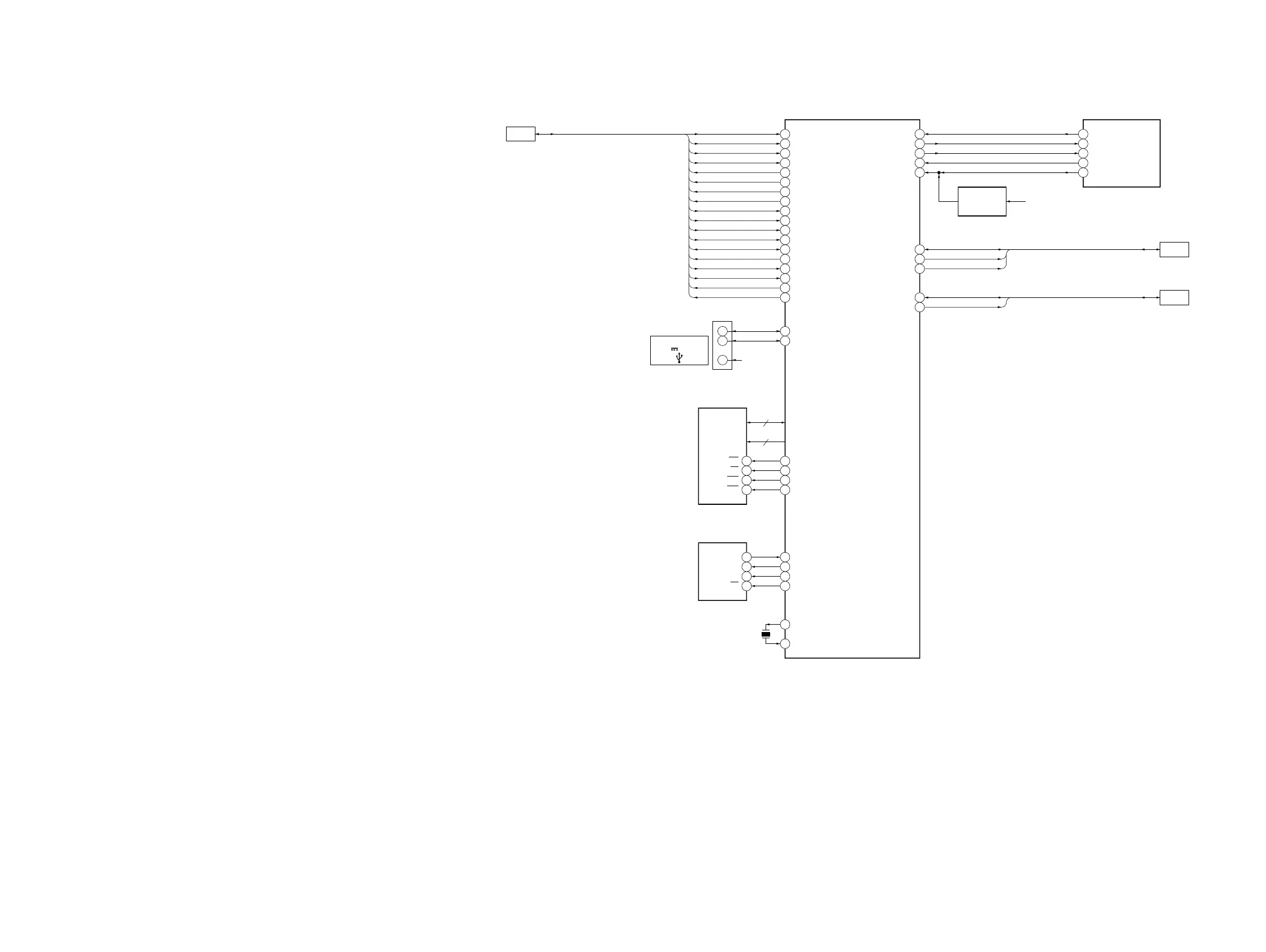

6-8. BLOCK DIAGRAM - NETWORK Section (2/2) -

ETHERNET CONTROLLER

IC6608 (1/2)

22

23

2

49

UART_MU/EU

135 T X D 0

HUB2_RESET

P6_RXD0

134 T X D 1

P6_RXD1

133 T X D 2

P6_RXD2

132 T X D 3

P6_RXD3

11 9 R X D 0

P6_OUTD[0]

11 8 R X D 1

P6_OUTD[1]

11 7 R X D 2

P6_OUTD[2]

11 6 R X D 3

P6_OUTD[3]

120 C R S _ D V

P6_OUTEN

123 REF_CLK

P6_OUTCLK

130 T C K

P6_RXCLK

136 T X _ E N

P6_RXDV

121 M D I O

MDIO_CPU

122 M D C

MDC_CPU

ETHEPHY_HUB1_RESET

137 ETHEPHY_HUB1_RESET

138 HUB2_RESET

107 U S B _ D +

106 U S B _ D –

VBUS

UART_EU/MU

ENDFLAG_EU_MU

INITX

>016B

P6_OUTD[0] – P6_OUTD[3], P6_RXD0 – P6_RXD3,

P6_OUTEN, P6_OUTCLK, P6_RXCLK, P6_RXDV,

MDIO_CPU, MDC_CPU, ETHEPHY_HUB1_INT,

HUB2_INT, ETHEPHY_HUB1_RESET, HUB2_RESET

HUB2_INT

7 HUB2_INTERRUPT

ETHEPHY_HUB1_INT

6 ETHPHY_HUB1_INTERRUPT

SYSTEM CONTROLLER

IC8002 (4/6)

109

11 0

105

106

MU-EU TX

MU-EU RX

ENDFLAG_EU_MU

RESET_MU_EU

69MD0 107 MODE0_MU_EU

102PROG_EU_RX

101PROG_EU_TX

RESET SIGNAL

GENERATOR

IC6605

+3.3V_FAN

S-RAM

IC6606

DATA0 – DATA15I/O0 – I/O15

A0 – A17 ADDR1 – ADDR18

16

14 WE

13 OE

16 BHE

15 BLE

18

WE

17

OE

41

BHE

40

BLE

39

SERIAL FLASH

IC6607

X1

71

X0

70

X6600

4MHz

26 FLASH_SIN

27 FLASH_SOT

28 FLASH_SCK

29 FLASH_CS

DO (IO1)

2

DI (IO0)

5

CLK

6

CS

1

UART_EU/SEL2

UART_SEL2/EU

>018B

UART_SEL2/EU, UART_EU/SEL2

19UART_SEL1/EU

20UART_EU/SEL1

3SEL_SEL1

UART_EU/SEL1

UART_SEL1/EU

SEL1_SEL

>017B

UART_SEL1/EU,

UART_EU/SEL1, SEL1_SEL

3

2

1

CN183

SETTING

DC5V 0.5A MAX

(Page 47)

(Page 47)

(Page 45)

Loading...

Loading...