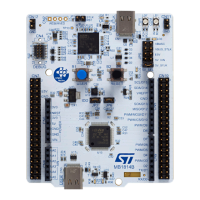

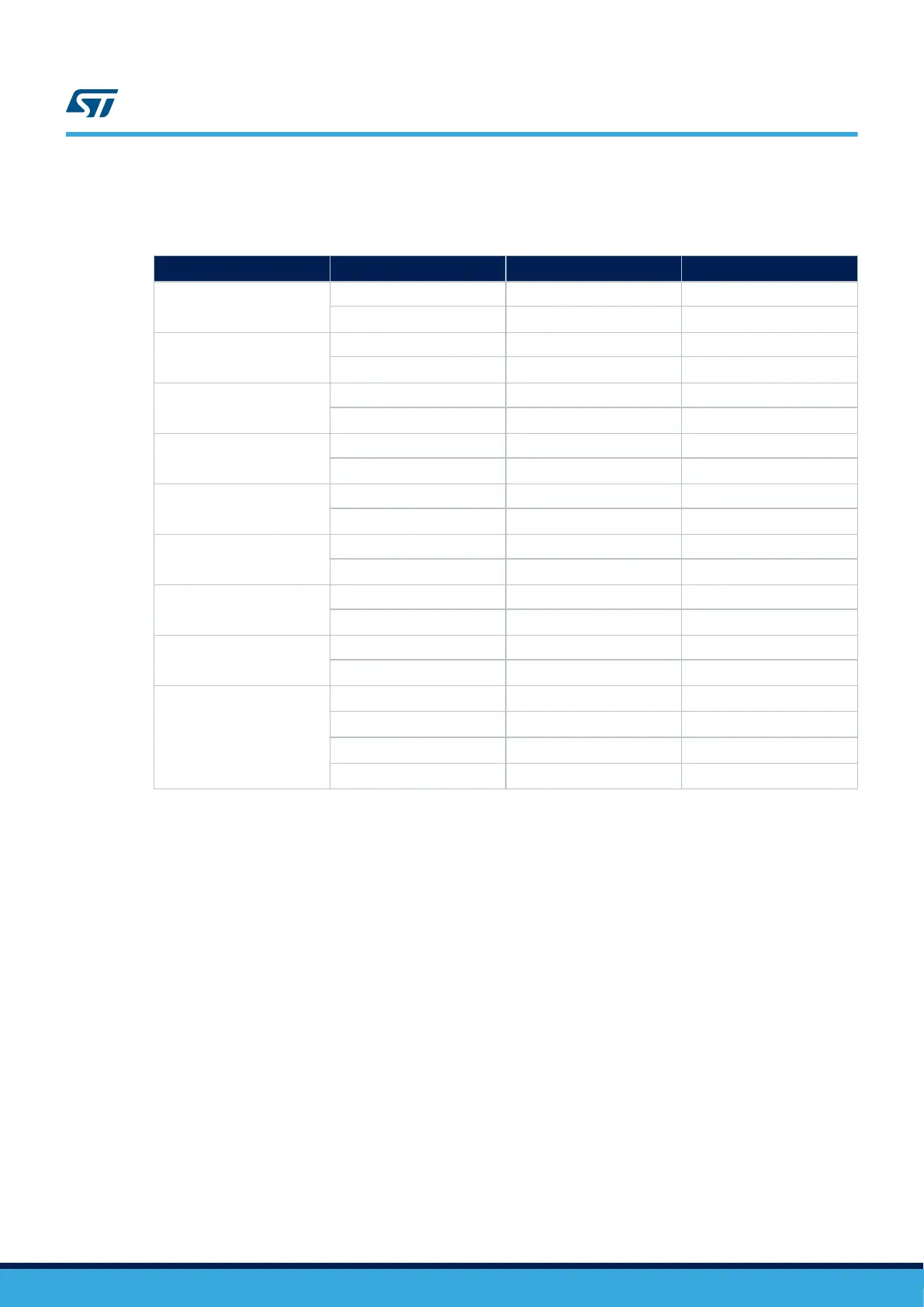

Hardware modifications are listed in Table 46 below:

Table 46. Configuration for SRAM A0-A5, A10-11 addresses, and command

Pin name Signal name Setting

SRAM

(1)

PF0

FMC_A0 R339 ON

OCSPI2_IO0 R98

OFF

(2)

PF1

FMC_A1 R335 ON

OCSPI2_IO1 R89

OFF

(2)

PF2

FMC_A2 R331 ON

OCSPI2_IO2 R82

OFF

(2)

PF3

FMC_A3 R74 ON

OCSPI2_IO3 R75

OFF

(2)

PG0

FMC_A10 R73 ON

OCSPI2_IO4 R76

OFF

(2)

PG1

FMC_A11 R333 ON

OCSPI2_IO5 R77

OFF

(2)

PF4

FMC_A4 R66 ON

OCSPI2_CLK R319

OFF

(2)

PF5

FMC_A5 R65 ON

OCSPI2_NCLK R318

OFF

(2)

PG10

FMC_NE3

(3)

R280 / JP2 ON / [1-2]

SDIO2_D1 R280 / JP2

OFF

(2)

/ OFF

OCSPI2_IO6 R115

OFF

(2)

DCMI_D2

(3)

R118

OFF

(2)

1. The default setting is in bold.

2. Remove to avoid stub if necessary.

3. PG10 signal is supplied by VDDMMC. Make sure to supply 3.3 V on VDDMMC (Refer to Section 6.3.5 )

Note: If using SD card 1 (Default configuration), use FMC_NE3 = PG10, then SD card 2 cannot be used). If using SD

card 2, use FMC_NE3 = PC8 by fitting JP12 [2-3], then SD card 1 cannot be used.

8.1.4 Limitations and hardware configuration for SRAM A19 (Just for the test)

Limitations with primary functions: Wi‑Fi

®

SPI.

Limitations with secondary functions: SAI1 and TRACE cannot be used.

UM2662

SRAM

UM2662 - Rev 1

page 51/95

Loading...

Loading...