www.ti.com

Oscillators and Clocks

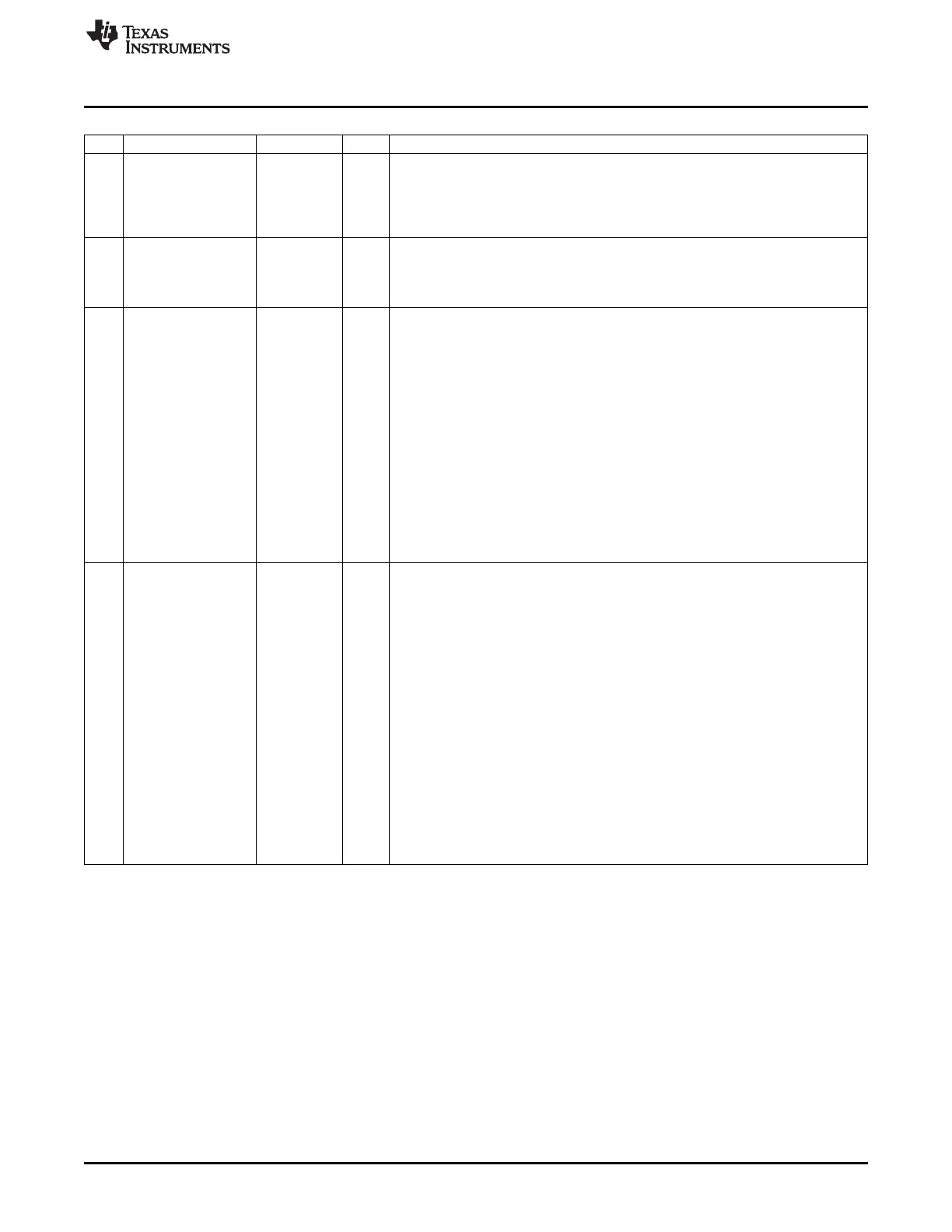

CLKCONCMD (0xC6) – Clock Control Command

Bit Name Reset R/W Description

7

OSC32K

1 R/W 32 kHz clock-source select. Setting this bit initiates a clock-source change only.

CLKCONSTA.OSC32K reflects the current setting. The 16 MHz RCOSC must be

selected as system clock when this bit is to be changed.

0: 32 kHz XOSC

1: 32 kHz RCOSC

6

OSC

1 R/W System clock-source select. Setting this bit initiates a clock-source change only.

CLKCONSTA.OSC reflects the current setting.

0: 32 MHz XOSC

1: 16 MHz RCOSC

5:3

TICKSPD[2:0]

001 R/W Timer ticks output setting. Cannot be higher than system clock setting given by OSC

bit setting.

000: 32 MHz

001: 16 MHz

010: 8 MHz

011: 4 MHz

100: 2 MHz

101: 1 MHz

110: 500 kHz

111: 250 kHz

Note that CLKCONCMD.TICKSPD can be set to any value, but the effect is

limited by the CLKCONCMD.OSC setting; i.e., if CLKCONCMD.OSC = 1 and

CLKCONCMD.TICKSPD = 000, CLKCONSTA.TICKSPD reads 001, and the

real TICKSPD is 16 MHz.

2:0

CLKSPD

001 R/W Clock speed. Cannot be higher than system clock setting given by the OSC bit

setting. Indicates current system-clock frequency

000: 32 MHz

001: 16 MHz

010: 8 MHz

011: 4 MHz

100: 2 MHz

101: 1 MHz

110: 500 kHz

111: 250 kHz

Note that CLKCONCMD.CLKSPD can be set to any value, but the effect is

limited by the CLKCONCMD.OSC setting; i.e., if

CLKCONCMD.OSC = 1 and CLKCONCMD.CLKSPD = 000,

CLKCONSTA.CLKSPD reads 001, and the real CLKSPD is 16 MHz.

Note also that the debugger cannot be used with a divided system clock. When

running the debugger, the value of CLKCONCMD.CLKSPD should be set to 000 when

CLKCONCMD.OSC = 0 or to 001 when CLKCONCMD.OSC = 1.

71

SWRU191C–April 2009–Revised January 2012 Power Management and Clocks

Submit Documentation Feedback

Copyright © 2009–2012, Texas Instruments Incorporated

Loading...

Loading...