112 www.xilinx.com 7 Series FPGAs GTP Transceivers User Guide

UG482 (v1.9) December 19, 2016

Chapter 3: Transmitter

Ports and Attributes

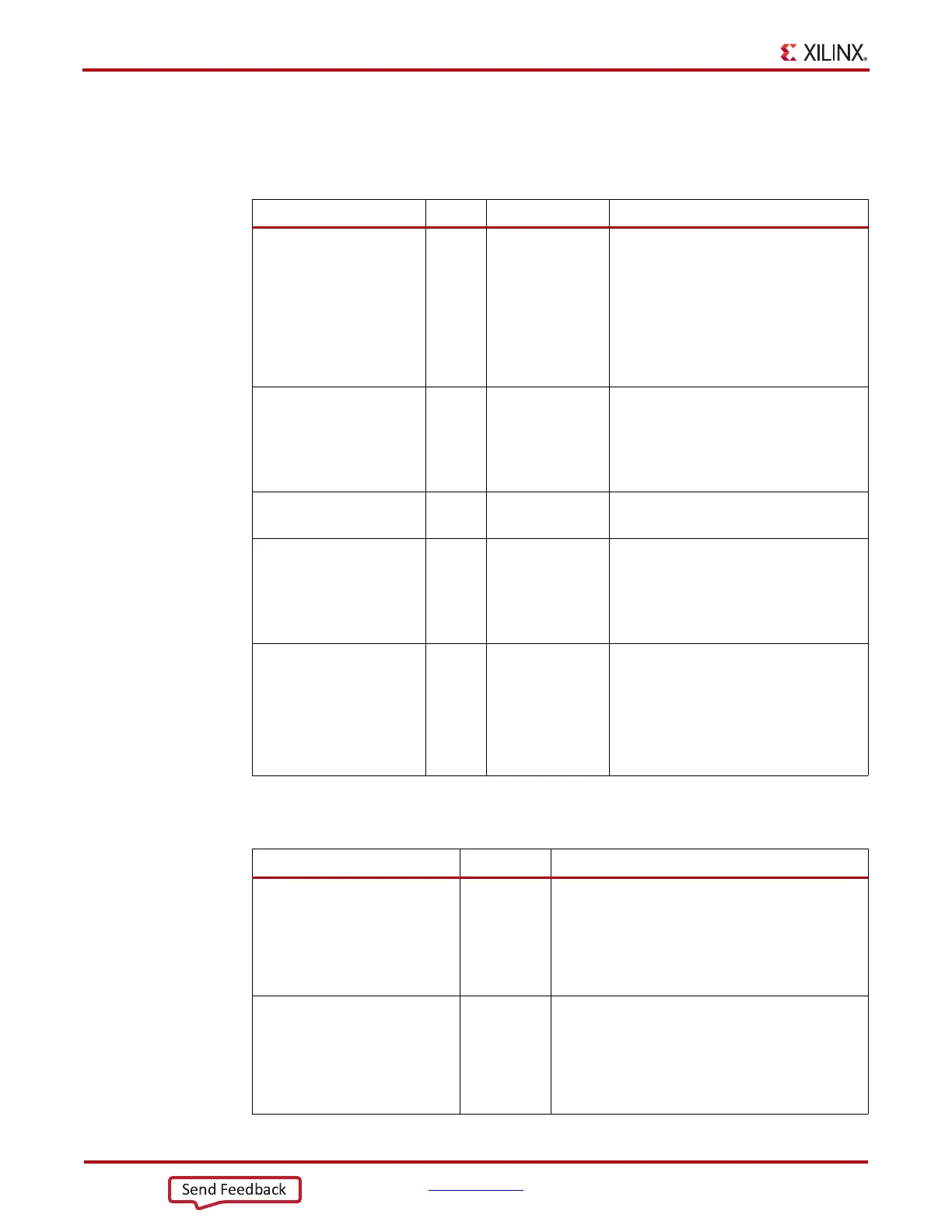

Table 3-26 defines the ports required for the TX phase interpolator PPM controller.

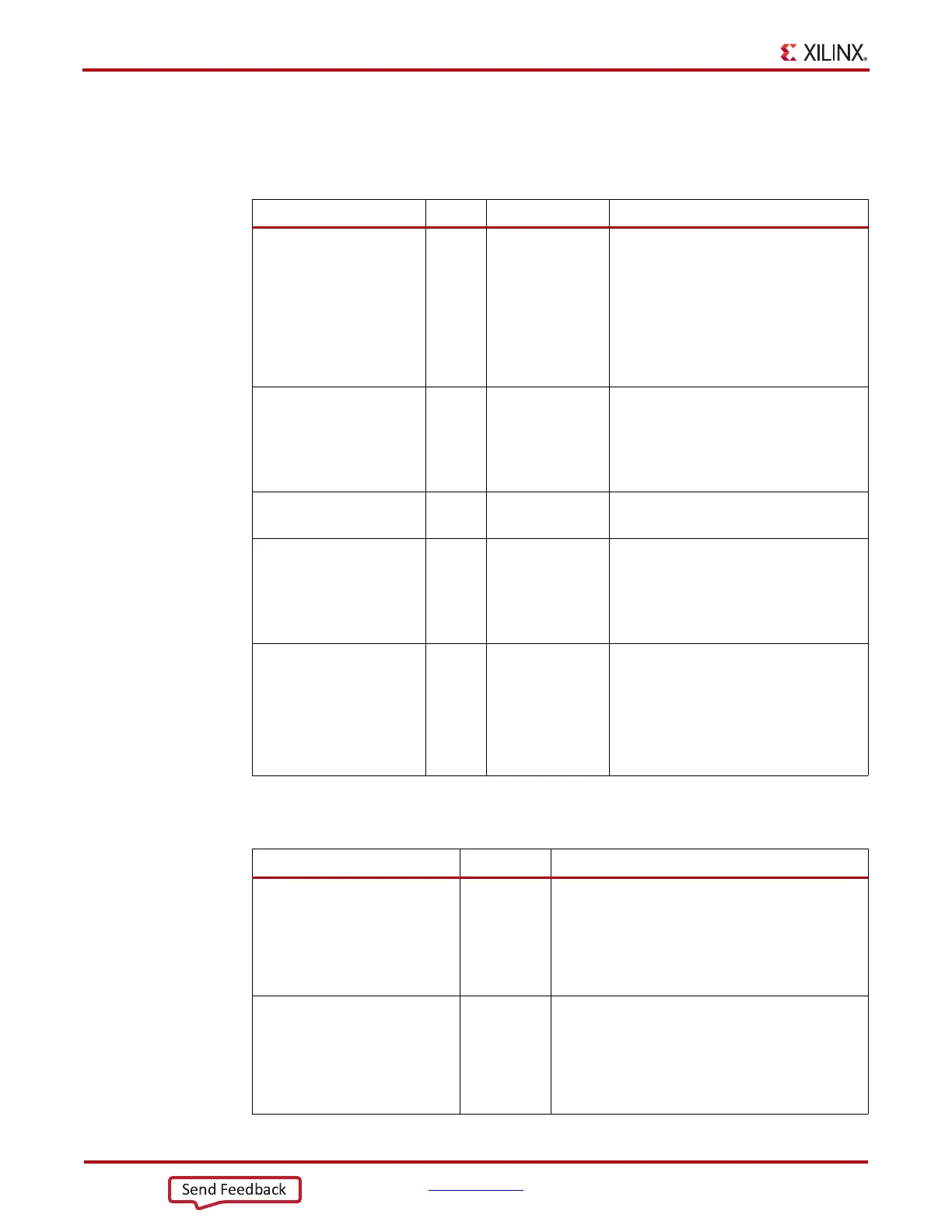

Table 3-27 defines the attributes required for the TX phase interpolator PPM controller.

Table 3-26: TX Phase Interpolator PPM Controller Ports

Port Dir Clock Domain Description

TXPIPPMEN In TXUSRCLK2 1'b0: Disables the TX Phase

Interpolator PPM Controller block. The

TX PI is not updated with a PI code and

retains the previous PI code.

1'b1: Enables the TX Phase Interpolator

PPM Controller block. The TX PI is

updated with a PI code every

TXPI_SYNFREQ_PPM[2:0] cycles.

TXPIPPMOVRDEN In TXUSRCLK2 1'b0: Normal operation.

1'b1: Enables direct control of the PI

code output to the TX PI in the TX PMA.

Use with TXPPMOVRD_VALUE[6:0] to

program the value of PI code.

TXPIPPMSEL In TXUSRCLK2 Reserved. This should always be tied to

1'b1.

TXPIPPMPD In Async 1'b0: Does not power down the TX

phase interpolator PPM controller

module.

1'b1: Powers down the TX phase

interpolator PPM controller module.

TXPIPPMSTEPSIZE[4:0] In TXUSRCLK2 TXPIPPMSTEPSIZE[4]:

1'b1: Increments PI code

1'b0: Decrements PI code

TXPIPPMSTEPSIZE[3:0] is the amount

to increment or decrement PI code. Its

values range from 0 to 15.

Table 3-27: TX Phase Interpolator PPM Controller Attributes

Attribute Type Description

TXPI_SYNFREQ_PPM[2:0] 3-bit Binary This attribute specifies how often PI code to the TX

PI is updated. It is updated every

(TXPI_SYNFREQ_PPM[2:0] + 1) cycles. All

values are valid except for 3'b000. The GT

Wizard's default value should be used for this

attribute.

TXPI_PPM_CFG[7:0] 8-bit Binary When TXPIPPMOVRDEN = 1'b1, the lower 7

bits of this attribute should be programmed to one of

the 128 values output to the TX PI. The most

significant bit needs to be pulsed (asserted High and

then Low) for the TX PI to register the new 7-bit

value of TXPI_PPM_CFG[6:0].

Loading...

Loading...