7 Series FPGAs GTP Transceivers User Guide www.xilinx.com 151

UG482 (v1.9) December 19, 2016

RX Margin Analysis

Eye Scan Theory

RXDATA is recovered from the equalized differential waveform by sampling after the RX

equalizer. The horizontal sampling position is determined by the CDR function and the vertical

position is differential zero. This is indicated as data sample in Figure 4-20.

To enable eye scan functionality, an additional sampler is provided with programmable (horizontal

and vertical) offsets from the data sample point. This is indicated as offset sample in Figure 4-20.

A single eye scan measurement consists of accumulating the number of data samples (sample count)

and the number of times that the offset sample disagreed with the data sample (error count). The bit

error ratio (BER) at the programmed vertical and horizontal offset is the ratio of the error count to

the sample count. The sample count can range from tens of thousands to greater than 10

14

.

Repeating such BER measurements for the full array of horizontal and vertical offsets (or a

subsampled set of offsets) produces a BER map as shown in Figure 4-20, commonly referred to as

a statistical eye, where the color map represents log

10

(BER). In this view, the eye is apparently

smaller than a traditional oscilloscope view (as in Figure 4-20) because it has been closed by very

low probability jitter and noise that does not show up in the much lower number of samples of an

oscilloscope.

Because this functionality puts no restrictions on the data patterns being received nor requires any

changes in the RX settings, it can be performed while application data is being received without

error. Furthermore, no FPGA logic is required—only the ability to read and write attributes.

Eye Scan Architecture

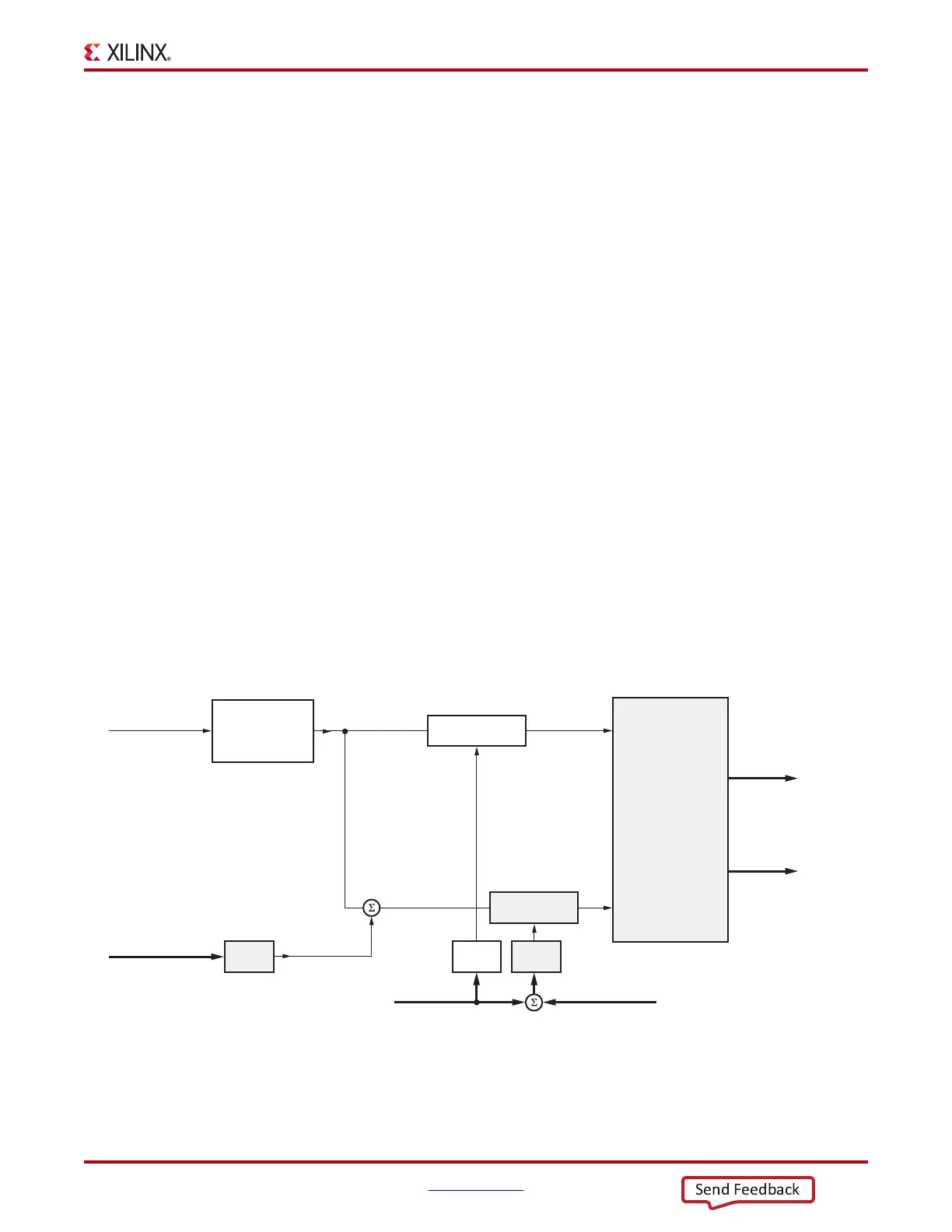

The blocks with shaded gray in Figure 4-21 describe the portion of the PMA architecture that

supports eye scan. The horizontal offset (HORZ_OFFSET) advances or delays the sampling time of

the offset samples relative to the data samples. The vertical offset (VERT_OFFSET) raises or lowers

the differential voltage threshold to which the equalized waveform is compared. The data samples

are deserialized into the Rdata bus, and the offset samples are deserialized into the Sdata bus.

X-Ref Target - Figure 4-21

Figure 4-21: PMA Architecture to Support Eye Scan

UG482_c4_10_112811

Capture FF

RX Input

Equalization

Error-detection,

Screening

De-serialization

PCS

Interface

Capture FF

+

DAC PI PI

VERT_OFFSET

Rec Clock HORZ_OFFSET

Rdata

Sdata

Loading...

Loading...