152 www.xilinx.com 7 Series FPGAs GTP Transceivers User Guide

UG482 (v1.9) December 19, 2016

Chapter 4: Receiver

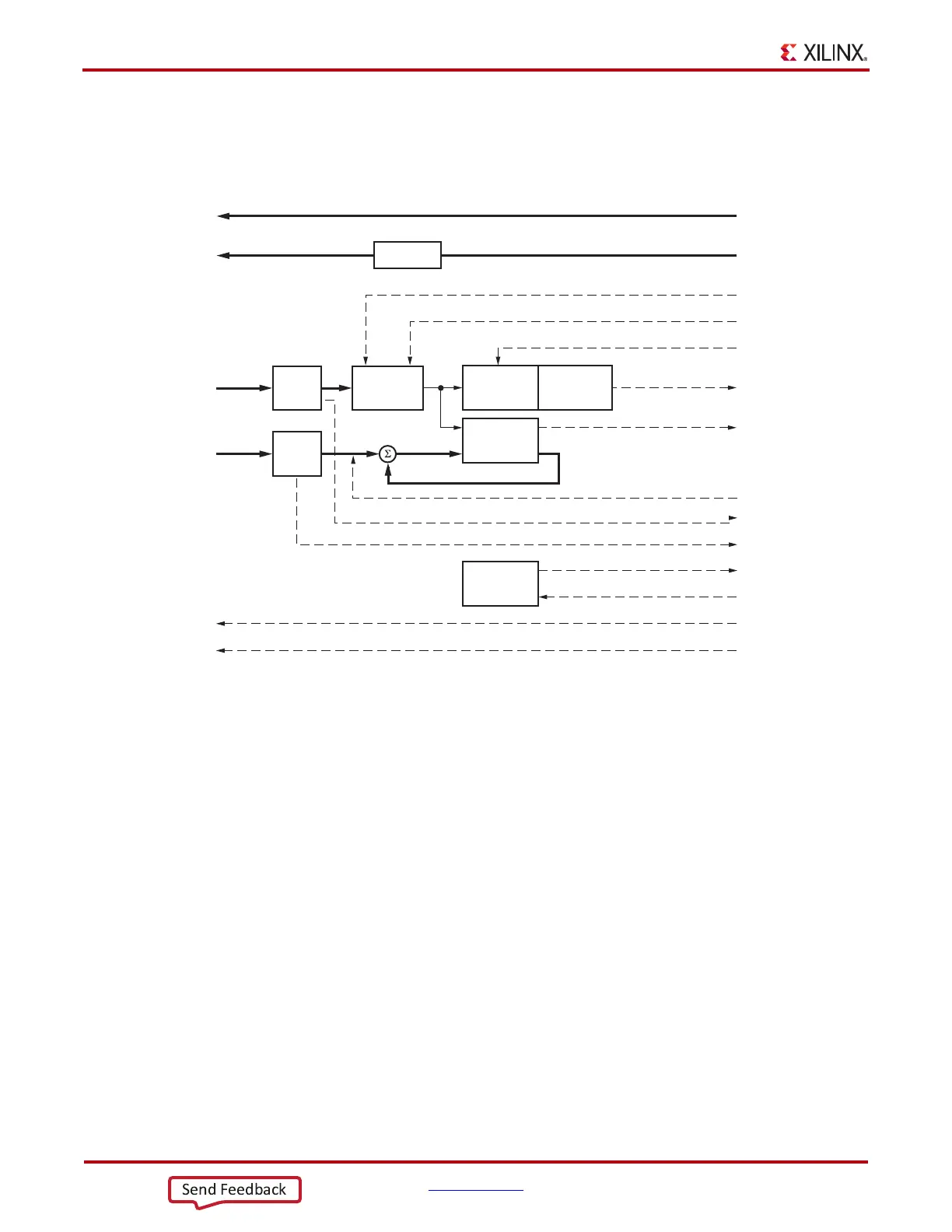

Figure 4-22 describes the portion of the PCS architecture that supports eye scan. The 40-bit Rdata

bus contains the data samples, and each bit of the 40-bit Sdata bus is one if and only if the

corresponding data sample and offset sample are not equal. (See ES_ERRDET_EN in Table 4-20,

page 155.)

Two consecutive cycles of Sdata are masked by ES_SDATA_MASK[79:0] (i.e., bit-by-bit Sdata[i]

AND NOT mask[i]). The algebraic sum of bits [39:0] of this result is the number of errors to be

added in the error counter.

Two consecutive cycles of Rdata are compared with the pattern in ES_QUALIFIER[79:0], and that

result is masked by (i.e., bit-by-bit ORed with) ES_QUAL_MASK[79:0]. The logical AND of this

result determines whether the prescaler/sample counter is incremented and the errors added to the

error counter. For a statistical eye, ES_QUAL_MASK is 80'b1, so the sample counter and error

counter accumulate on every cycle. ES_SDATA_MASK unmasks only the current data (bit 39 and

below; see the description of RX_DATA_WIDTH) to avoid double counting errors because they

appear first in the lower 40 bits and then in the upper 40 bits on the next cycle.

Alternate use modes produce scope-like displays by unmasking a sequence of Rdata bits (up to 20),

causing error and sample accumulation only if Rdata matches ES_QUALIFIER in that range of bits.

In these use modes, only one Sdata bit per measurement is unmasked. In diagnostic use modes,

Rdata and Sdata are frozen and can be read out through the DRP interface when:

• An error occurs,

• A count qualifier occurs,

• A fabric port causes a trigger, or

• A trigger is forced via an attribute write.

X-Ref Target - Figure 4-22

Figure 4-22: PCS Architecture to Support Eye Scan

UG482_c4_11_041012

Rdata

ES_VERT_OFFSET

ES_QUALIFIER

ES_QUAL_MASK

ES_PRESCALE

es_sample_count

es_error_count

es_rdata

es_sdata

es_control_status

ES_CONTROL

ES_ERRDET_EN

ES_EYE_SCAN_EN

ES_SDATA_MASK

ES_HORZ_OFFSET

Filter

Count

Qualifier

FIFO

Sdata

FIFO

Prescaler

DRP

Interface

PMA

Interface

Error

Counter

State

Machine

Sample

Counter

Loading...

Loading...