7 Series FPGAs GTP Transceivers User Guide www.xilinx.com 177

UG482 (v1.9) December 19, 2016

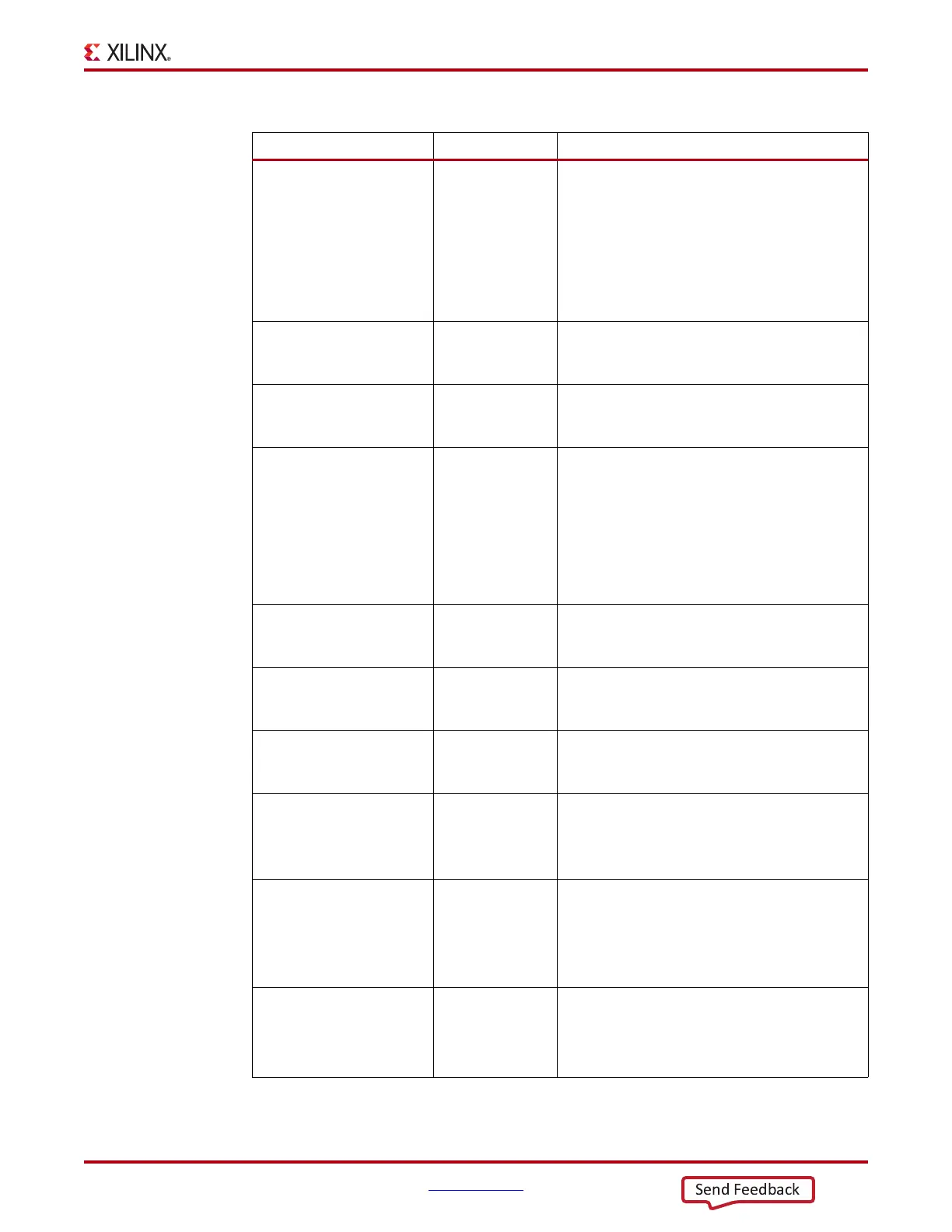

RX Buffer Bypass

RX_XCLK_SEL String Selects the clock source used to drive the RX

parallel clock domain (XCLK).

RXREC: Selects the RX recovered clock as

source of XCLK. Used when using the RX

elastic buffer.

RXUSR: Selects RXUSRCLK as the source of

XCLK. Used when bypassing the RX elastic

buffer.

RXPH_CFG 24-bit Binary Reserved. The recommended value from the

7 Series FPGAs Transceivers Wizard should be

used.

RXPH_MONITOR_SEL 5-bit Binary Reserved. The recommended value from the

7 Series FPGAs Transceivers Wizard should be

used.

RXPHDLY_CFG 24-bit Binary RX phase and delay alignment configuration.

RXPHDLY_CFG[19] = 1 is used to set the RX

delay alignment tap to the full range of ±4 ns.

RXPHDLY_CFG[19] = 0 is used to set the RX

delay alignment tap to the half range of ±2 ns.

Reserved. The recommended value from the

7 Series FPGAs Transceivers Wizard should be

used.

RXDLY_CFG 16-bit Binary Reserved. The recommended value from the

7 Series FPGAs Transceivers Wizard should be

used.

RXDLY_LCFG 9-bit Binary Reserved. The recommended value from the

7 Series FPGAs Transceivers Wizard should be

used.

RXDLY_TAP_CFG 16-bit Binary Reserved. The recommended value from the

7 Series FPGAs Transceivers Wizard should be

used.

RX_DDI_SEL 6-bit Binary RX data delay insertion select.

Reserved. The recommended value from the

7 Series FPGAs Transceivers Wizard should be

used.

RXSYNC_MULTILANE 1-bit Binary Indicates whether the lane is used as part of a

multi-lane interface. Only valid on RX buffer

bypass master lane in auto mode.

0: This lane is used in single-lane mode.

1: This lane is used in multi-lane mode.

RXSYNC_SKIP_DA 1-bit Binary Control to skip delay alignment procedure. Only

valid on buffer bypass master lane in auto mode.

0: RX delay alignment procedure occurs.

1: RX delay alignment procedure is skipped.

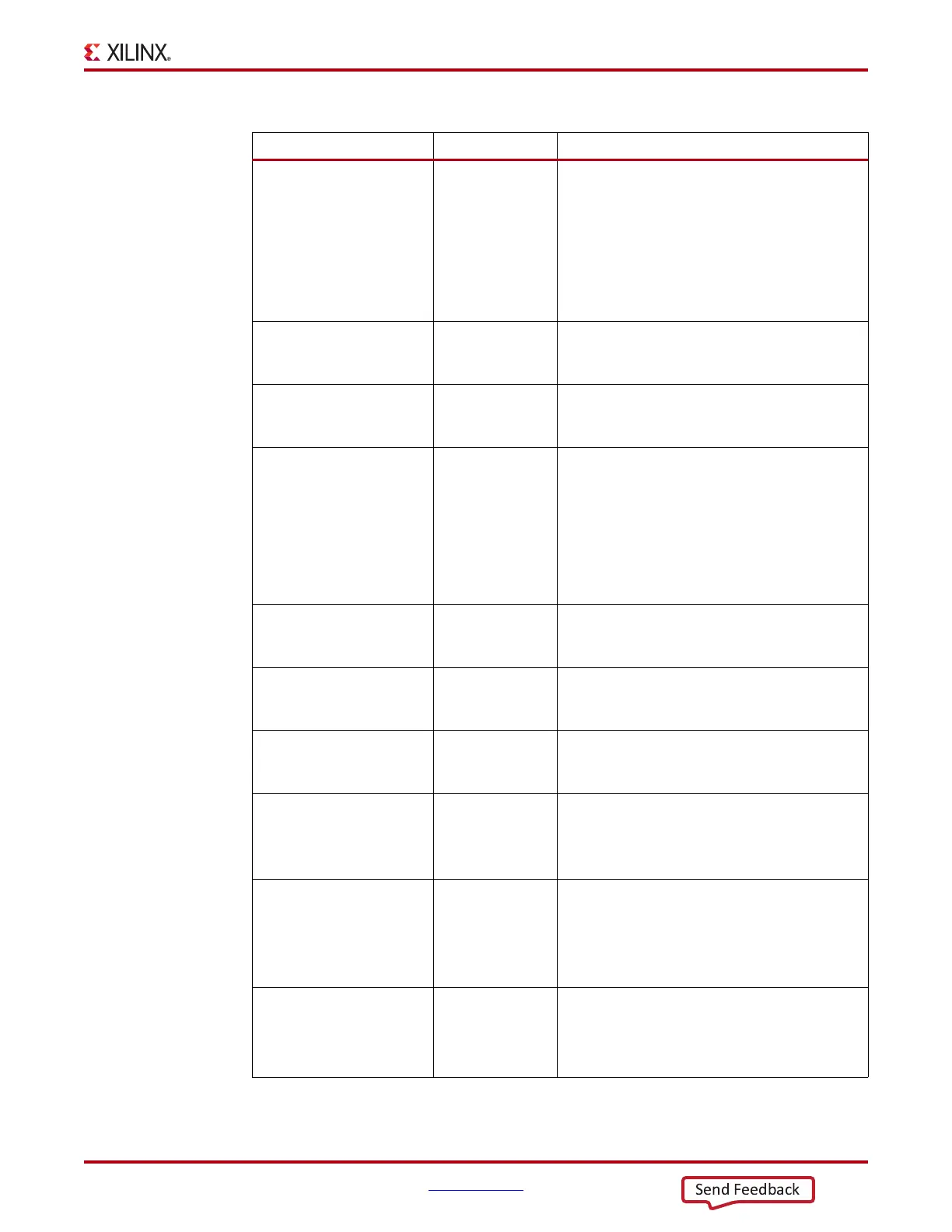

Table 4-30: RX Buffer Bypass Attributes (Cont’d)

Attribute Type Description

Loading...

Loading...