178 www.xilinx.com 7 Series FPGAs GTP Transceivers User Guide

UG482 (v1.9) December 19, 2016

Chapter 4: Receiver

RX Buffer Bypass Use Modes

RX phase alignment can be performed on one channel (single lane) or a group of channels sharing

a single RXOUTCLK (multi-lane). For GTP transceivers, RX buffer bypass supports single-lane

auto mode, and multi-lane applications in manual and auto mode (Table 4-31).

Using RX Buffer Bypass in Single-Lane Auto Mode

These GTP transceiver settings should be used to bypass the RX buffer:

• RXBUF_EN = FALSE.

• RX_XCLK_SEL = RXUSR.

• RXOUTCLKSEL = 010b to select the RX recovered clock as the source of RXOUTCLK.

• RXDDIEN = 1.

With the RX recovered clock selected, RXOUTCLK is to be used as the source of RXUSRCLK.

The user must ensure that RXOUTCLK and the selected RX recovered clock are running and

operating at the desired frequency. When the RX elastic buffer is bypassed, the RX phase alignment

procedure must be performed after these conditions:

• Resetting or powering up the GTP receiver.

• Resetting or powering up the PLL.

• Changing the RX recovered clock source or frequency.

• Changing the GTP RX line rate.

To set up RX buffer bypass in single-lane auto mode, these attributes should be set:

• RXSYNC_MULTILANE = 0

• RXSYNC_OVRD = 0

Set the ports as per Figure 4-36.

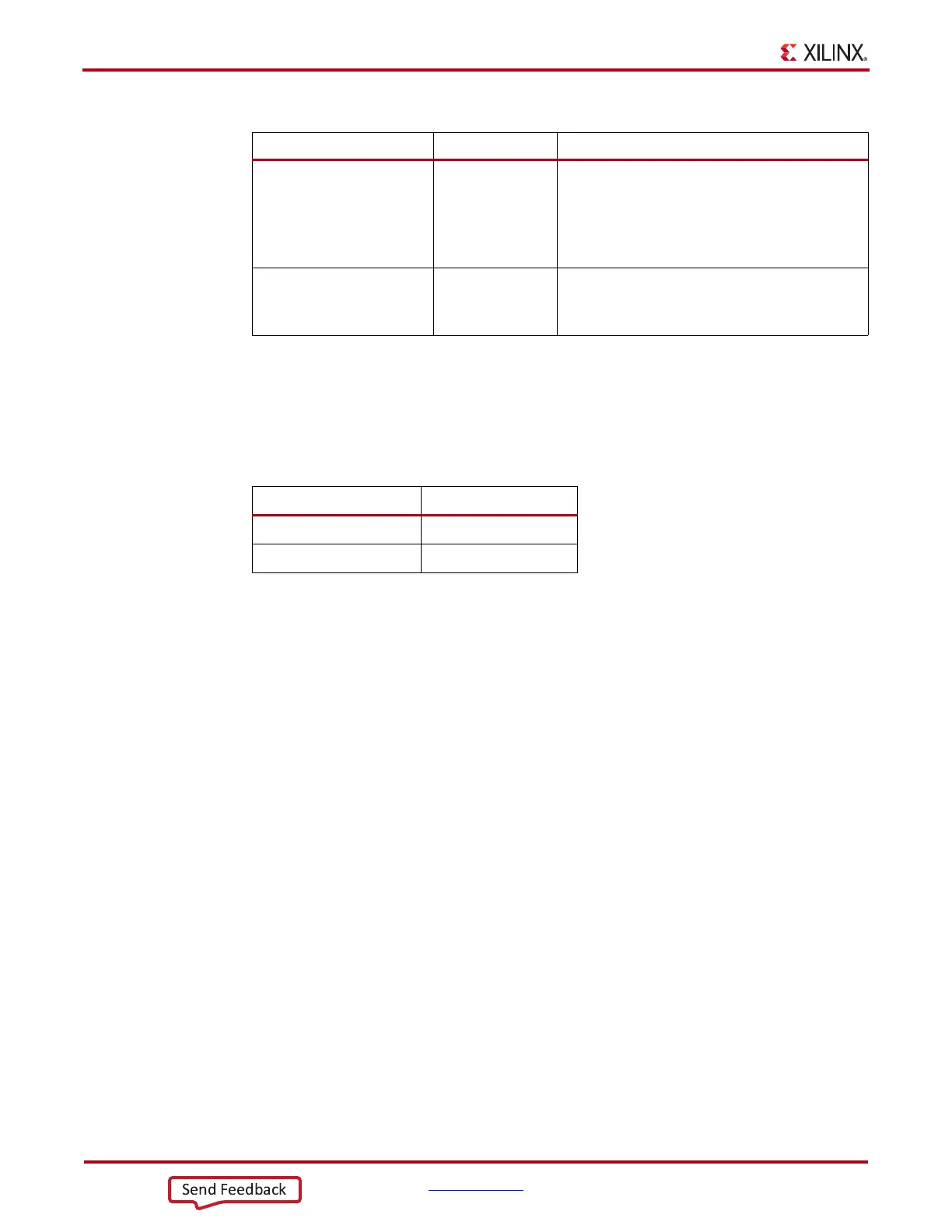

RXSYNC_OVRD 1-bit Binary Manual mode override.

0: RX Buffer bypass auto mode is enabled.

1: RX Buffer bypass manual mode is used. RX

Buffer bypass control is implemented in fabric

logic.

TST_RSV[0] 1-bit Binary 0: Normal.

1: Override data delay insertion (DDI) delay

setting with RX_DDI_SEL attribute.

Table 4-30: RX Buffer Bypass Attributes (Cont’d)

Attribute Type Description

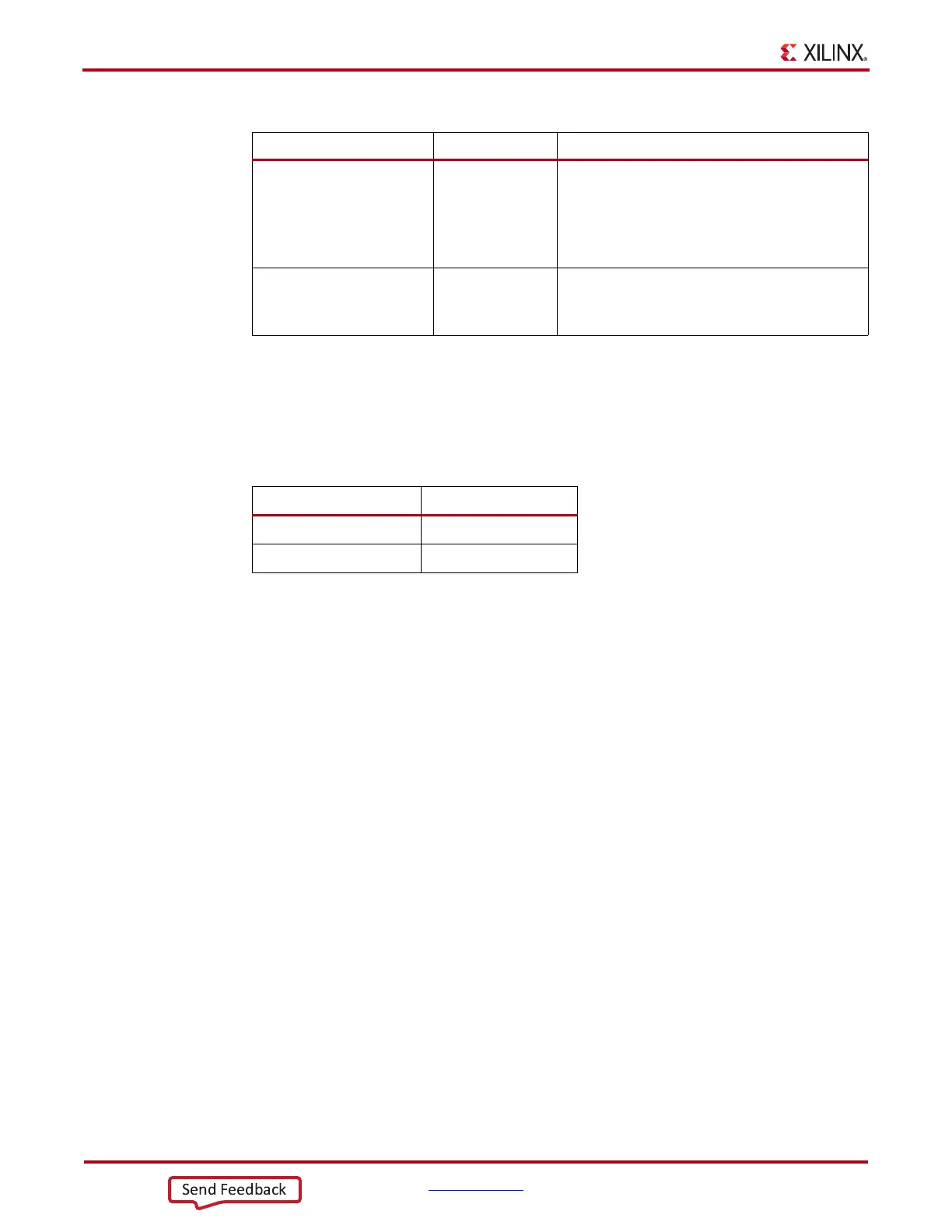

Table 4-31: RX Buffer Bypass Use Modes

Rx Buffer Bypass GTP Transceiver

Single-Lane Auto

Multi-Lane Manual or Auto

Loading...

Loading...