7 Series FPGAs GTP Transceivers User Guide www.xilinx.com 231

UG482 (v1.9) December 19, 2016

Power Supply and Filtering

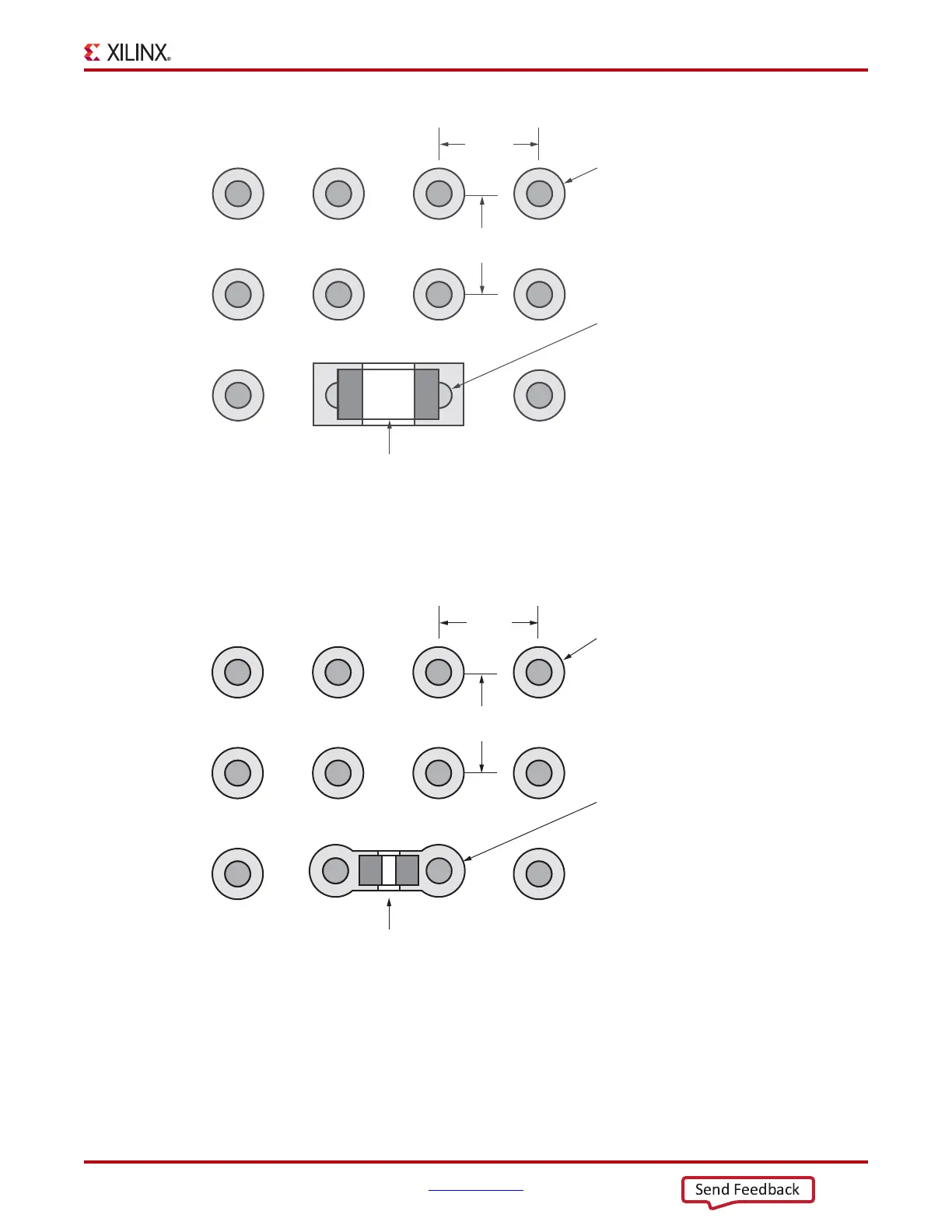

Another option is to use an 0201 capacitor and mounting it between the vias. An example of this is

shown in Figure 5-11.

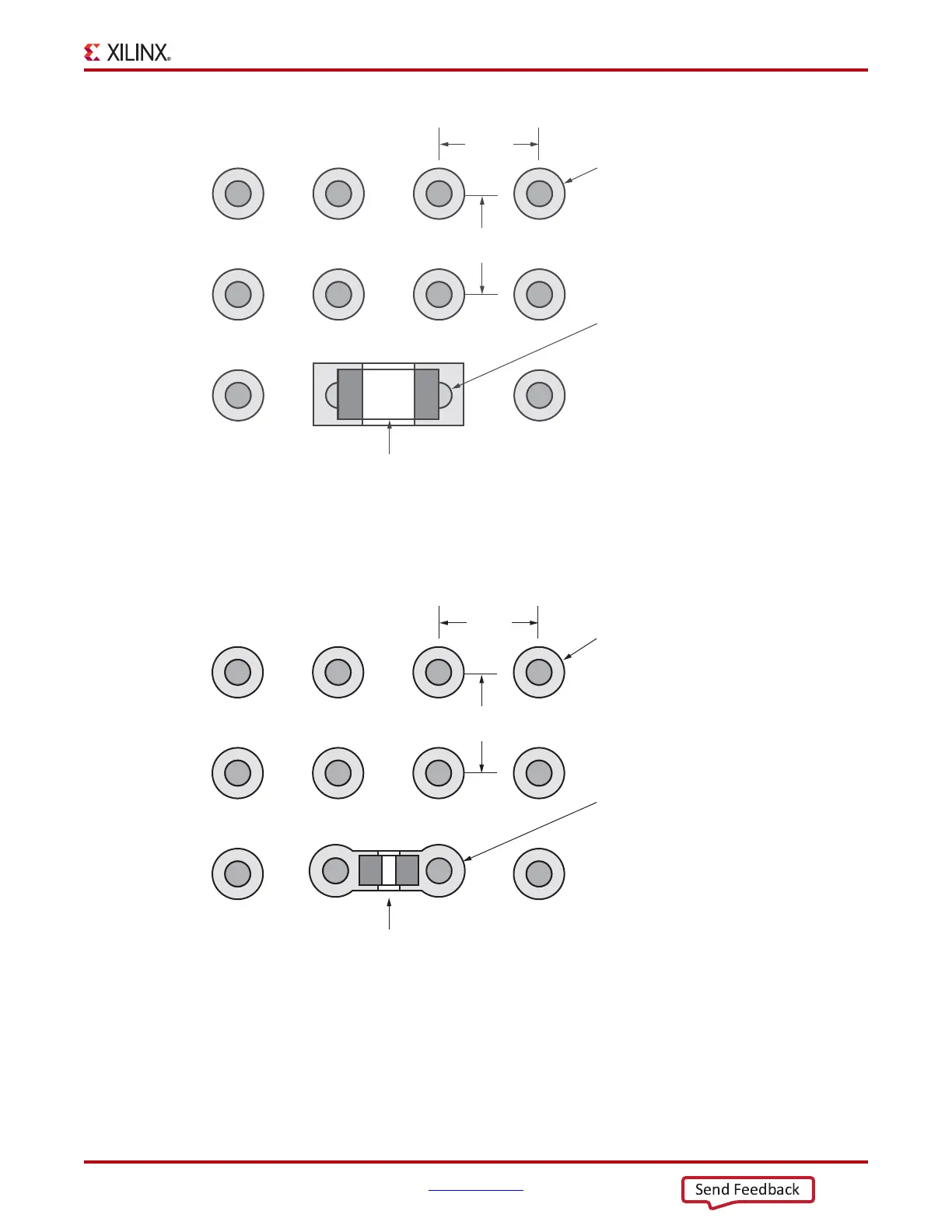

X-Ref Target - Figure 5-10

Figure 5-10: Placement of 0.1 µF 0402 Capacitor Using Filled Via in Pad Under FPGA

1 mm.

BGA Pin Field Vias

Filled Via in Pad

0402 Capacitor

1 mm.View From Bottom of PCB

UG482_c5_10_072412

X-Ref Target - Figure 5-11

Figure 5-11: Placement of 0.1 µF 0201 Capacitor Using Filled Via in Pad Under FPGA

1 mm.

BGA Pin Field Vias

Filled Via in Pad

0201 Capacitor

1 mm.View From Bottom of PCB

UG482_c5_11_072412

Loading...

Loading...