7 Series FPGAs GTP Transceivers User Guide www.xilinx.com 287

UG482 (v1.9) December 19, 2016

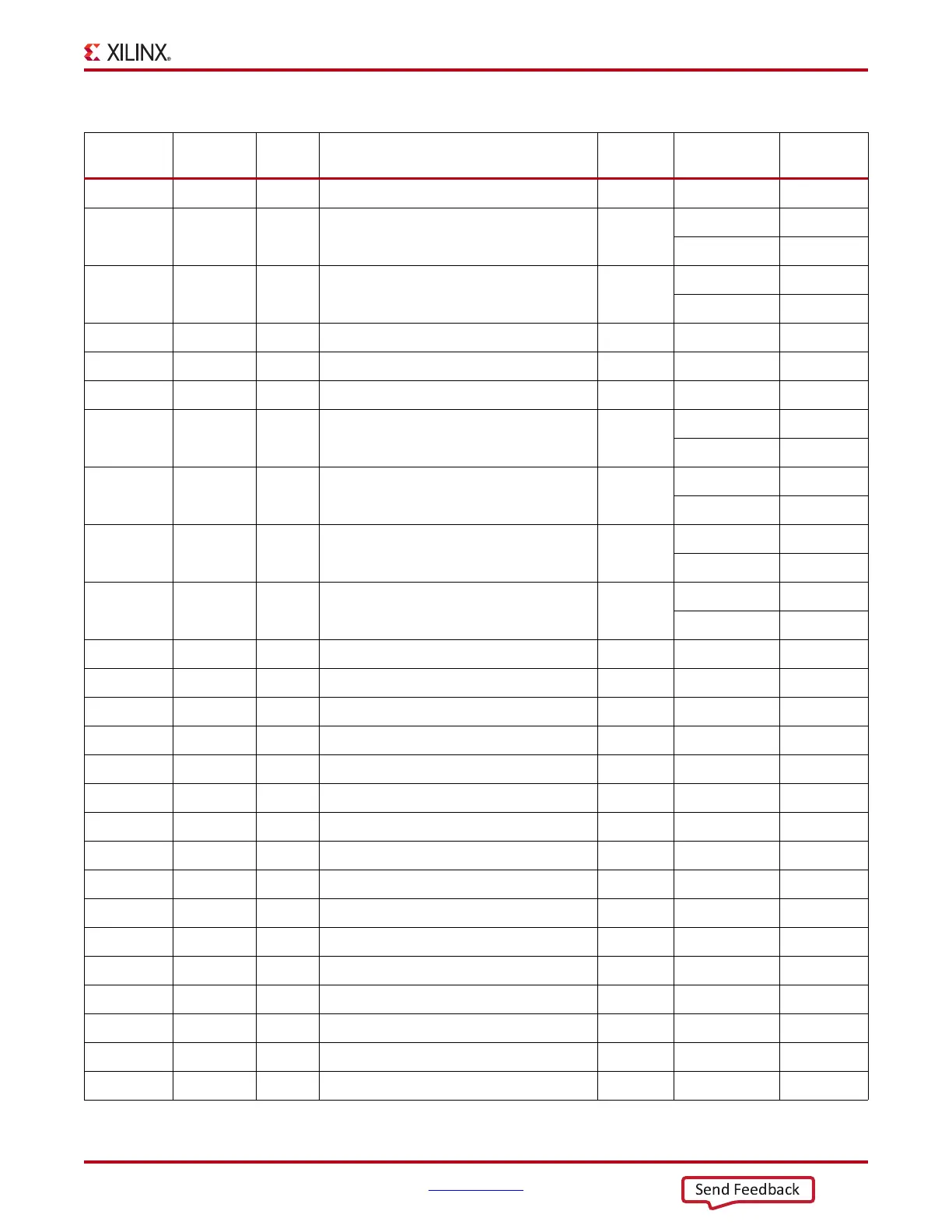

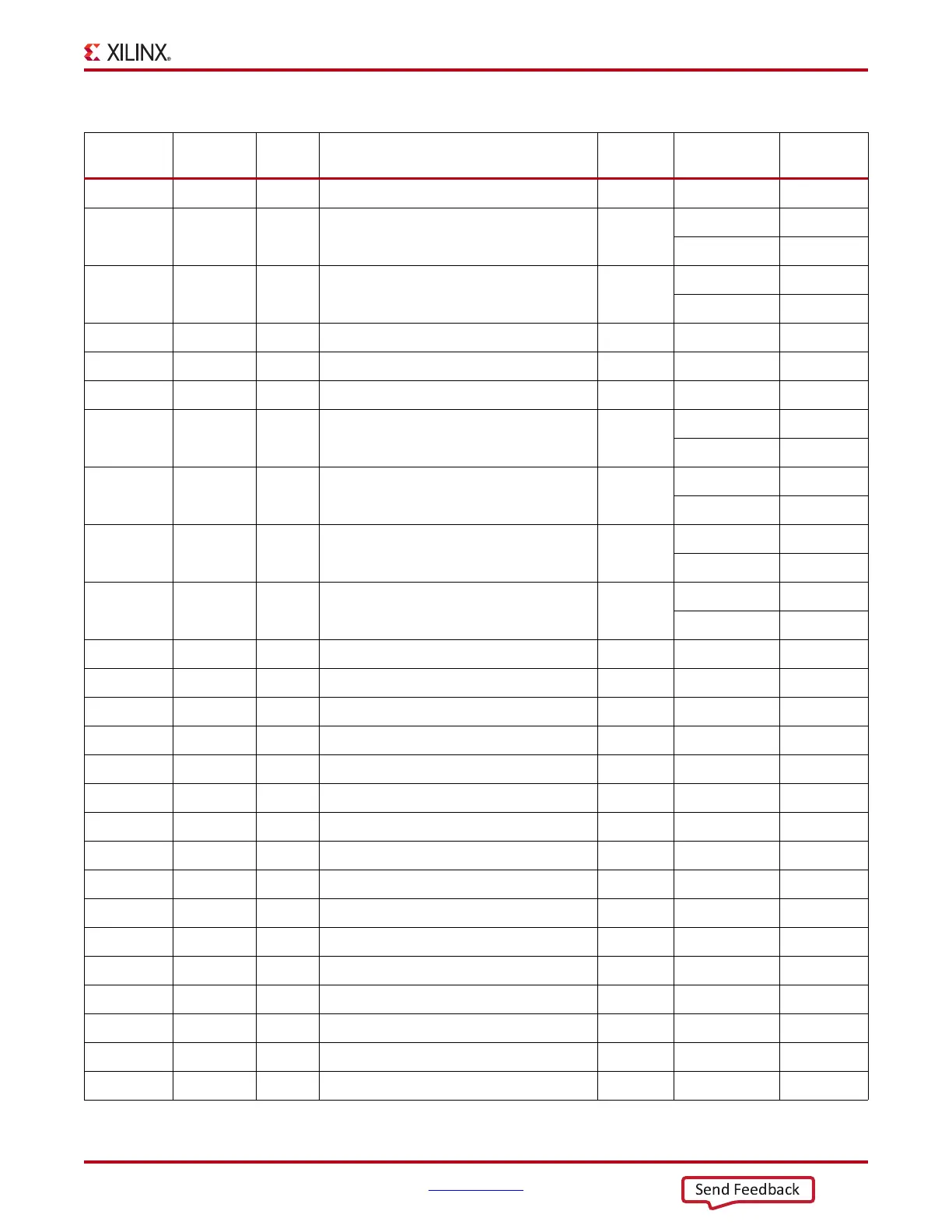

0019 8:6 R/W TX_EIDLE_ASSERT_DELAY 2:0 0-7 0-7

0019 5 R/W TX_LOOPBACK_DRIVE_HIZ 0

FALSE 0

TRUE 1

0019 4:0 R/W TX_DRIVE_MODE 0

DIRECT 0

PIPE 1

001A 15:8 R/W PD_TRANS_TIME_TO_P2 7:0 0-255 0-255

001A 7:0 R/W PD_TRANS_TIME_NONE_P2 7:0 0-255 0-255

001B 12:1 R/W PD_TRANS_TIME_FROM_P2 11:0 0-4095 0-4095

001B 0 R/W PCS_PCIE_EN 0

FALSE 0

TRUE 1

001C 15 R/W TXBUF_RESET_ON_RATE_CHANGE 0

FALSE 0

TRUE 1

001C 14 R/W TXBUF_EN 0

FALSE 0

TRUE 1

001C 5 R/W TXGEARBOX_EN 0

FALSE 0

TRUE 1

001C 2:0 R/W GEARBOX_MODE 2:0 0-7 0-7

001E 14 R/W RXLPM_HOLD_DURING_EIDLE 0 0-1 0-1

0024 12:0 R/W RX_OS_CFG 12:0 0-8191 0-8191

002A 15:14 R/W RXLPM_LF_CFG 17:16 0-3 0-3

002A 13:0 R/W RXLPM_HF_CFG 13:0 0-16383 0-16383

002B 15:0 R/W RXLPM_LF_CFG 15:0 0-65535 0-65535

002C 15:0 R/W ES_QUALIFIER 15:0 0-65535 0-65535

002D 15:0 R/W ES_QUALIFIER 31:16 0-65535 0-65535

002E 15:0 R/W ES_QUALIFIER 47:32 0-65535 0-65535

002F 15:0 R/W ES_QUALIFIER 63:48 0-65535 0-65535

0030 15:0 R/W ES_QUALIFIER 79:64 0-65535 0-65535

0031 15:0 R/W ES_QUAL_MASK 15:0 0-65535 0-65535

0032 15:0 R/W ES_QUAL_MASK 31:16 0-65535 0-65535

0033 15:0 R/W ES_QUAL_MASK 47:32 0-65535 0-65535

0034 15:0 R/W ES_QUAL_MASK 63:48 0-65535 0-65535

0035 15:0 R/W ES_QUAL_MASK 79:64 0-65535 0-65535

Table D-2: DRP Map of GTPE2_CHANNEL Primitive (Cont’d)

DRP

Address

DRP Bits R/W Attribute Name

Attribute

Bits

Attribute

Encoding

DRP

Encoding

Loading...

Loading...