288 www.xilinx.com 7 Series FPGAs GTP Transceivers User Guide

UG482 (v1.9) December 19, 2016

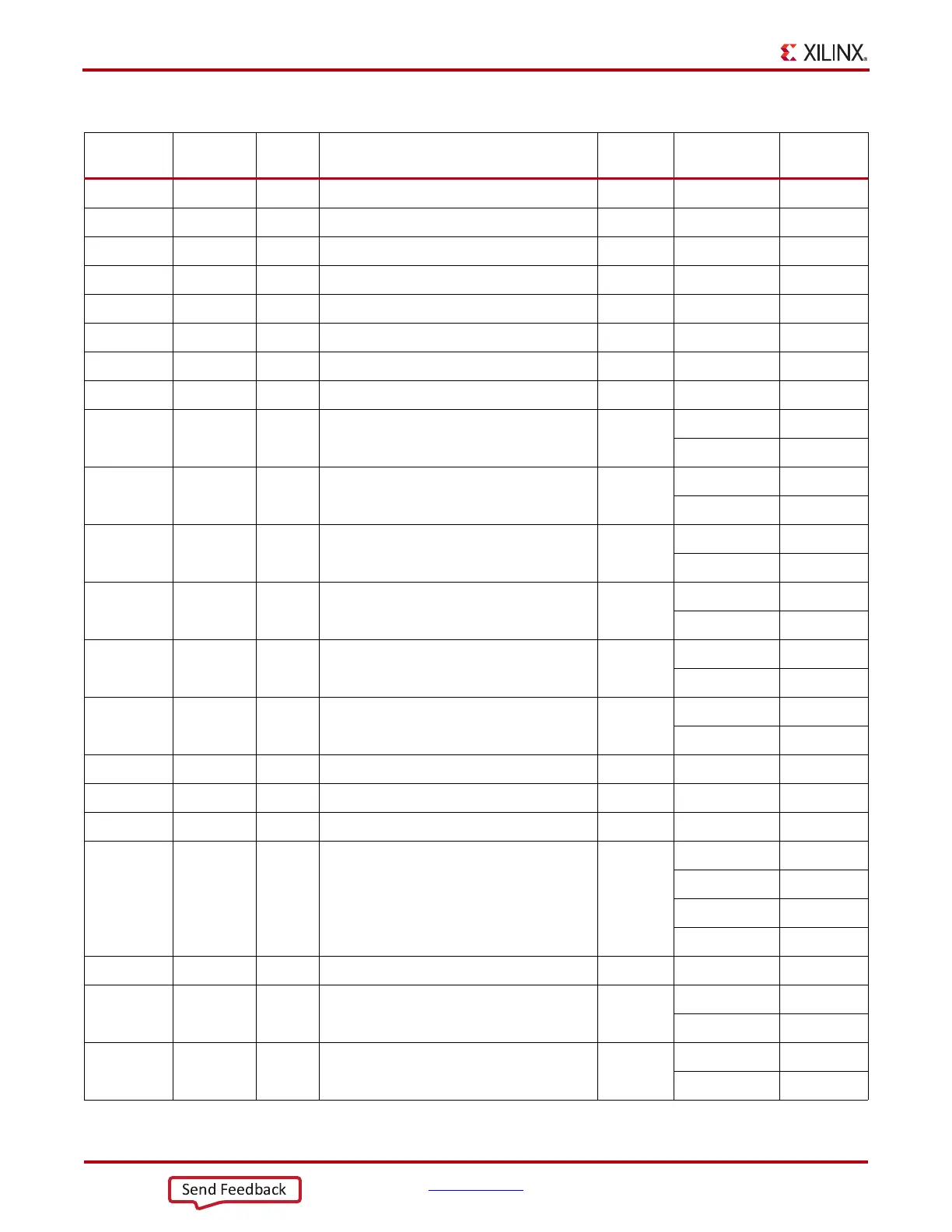

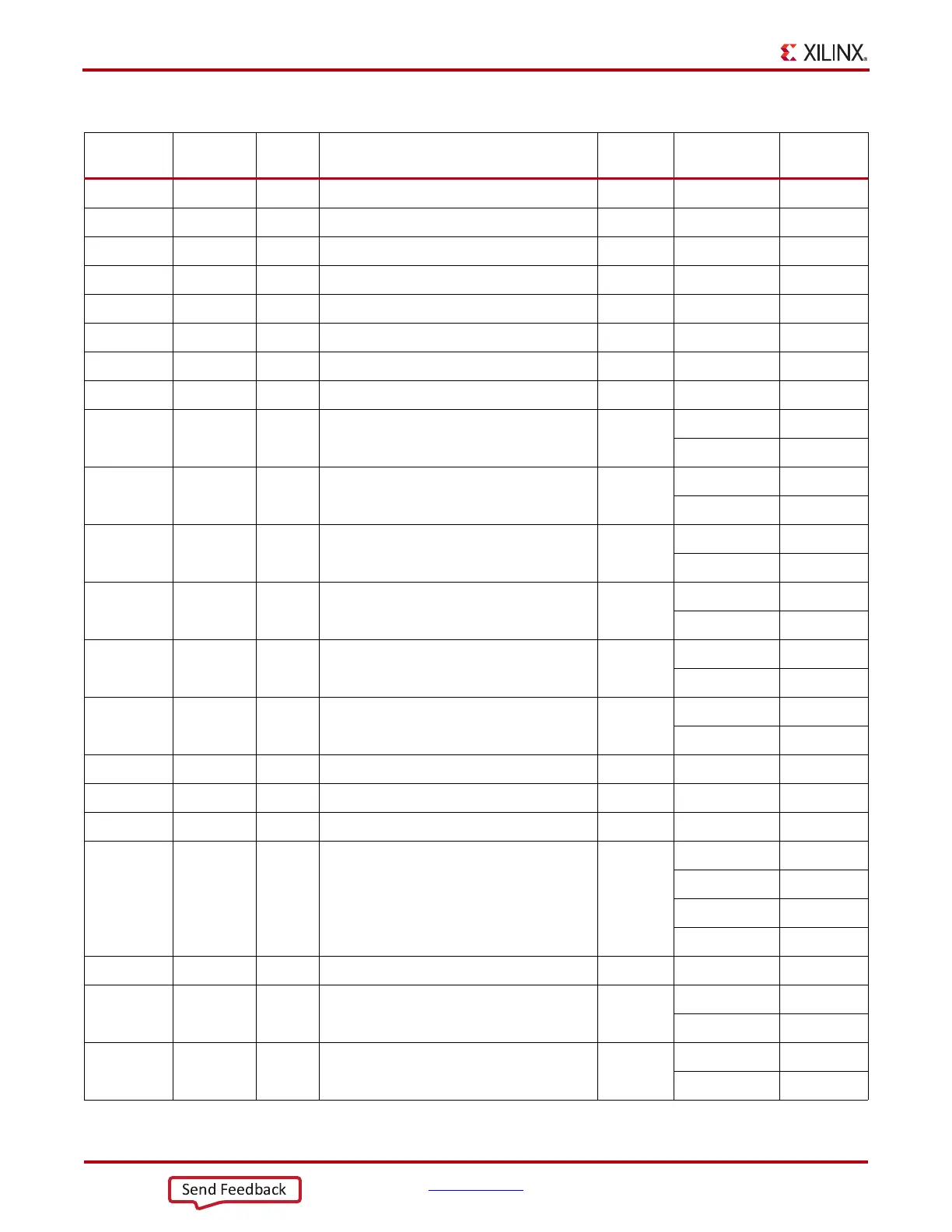

Appendix D: DRP Address Map of the GTP Transceiver

0036 15:0 R/W ES_SDATA_MASK 15:0 0-65535 0-65535

0037 15:0 R/W ES_SDATA_MASK 31:16 0-65535 0-65535

0038 15:0 R/W ES_SDATA_MASK 47:32 0-65535 0-65535

0039 15:0 R/W ES_SDATA_MASK 63:48 0-65535 0-65535

003A 15:0 R/W ES_SDATA_MASK 79:64 0-65535 0-65535

003B 15:11 R/W ES_PRESCALE 4:0 0-31 0-31

003B 8:0 R/W ES_VERT_OFFSET 8:0 0-511 0-511

003C 11:0 R/W ES_HORZ_OFFSET 11:0 0-4095 0-4095

003D 15 R/W RX_DISPERR_SEQ_MATCH 0

FALSE 0

TRUE 1

003D 14 R/W DEC_PCOMMA_DETECT 0

FALSE 0

TRUE 1

003D 13 R/W DEC_MCOMMA_DETECT 0

FALSE 0

TRUE 1

003D 12 R/W DEC_VALID_COMMA_ONLY 0

FALSE 0

TRUE 1

003D 9 R/W ES_ERRDET_EN 0

FALSE 0

TRUE 1

003D 8 R/W ES_EYE_SCAN_EN 0

FALSE 0

TRUE 1

003D 5:0 R/W ES_CONTROL 5:0 0-63 0-63

003E 9:0 R/W ALIGN_COMMA_ENABLE 9:0 0-1023 0-1023

003F 9:0 R/W ALIGN_MCOMMA_VALUE 9:0 0-1023 0-1023

0040 15:14 R/W RXSLIDE_MODE 1:0

OFF 0

AUTO 1

PCS 2

PMA 3

0040 9:0 R/W ALIGN_PCOMMA_VALUE 9:0 0-1023 0-1023

0041 14:13 R/W ALIGN_COMMA_WORD 1:0

11

22

0041 12:8 R/W RX_SIG_VALID_DLY 4:0

10

21

Table D-2: DRP Map of GTPE2_CHANNEL Primitive (Cont’d)

DRP

Address

DRP Bits R/W Attribute Name

Attribute

Bits

Attribute

Encoding

DRP

Encoding

Loading...

Loading...