290 www.xilinx.com 7 Series FPGAs GTP Transceivers User Guide

UG482 (v1.9) December 19, 2016

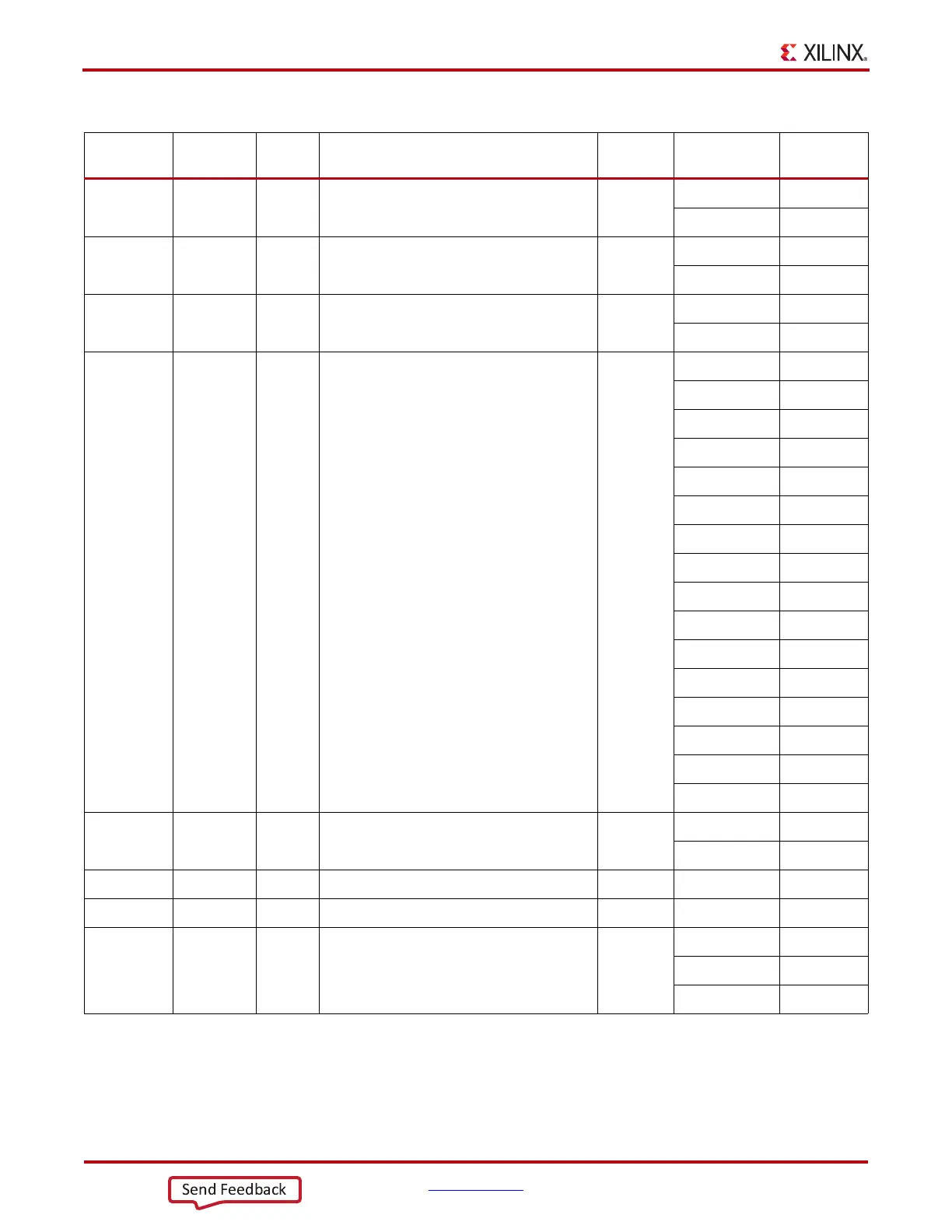

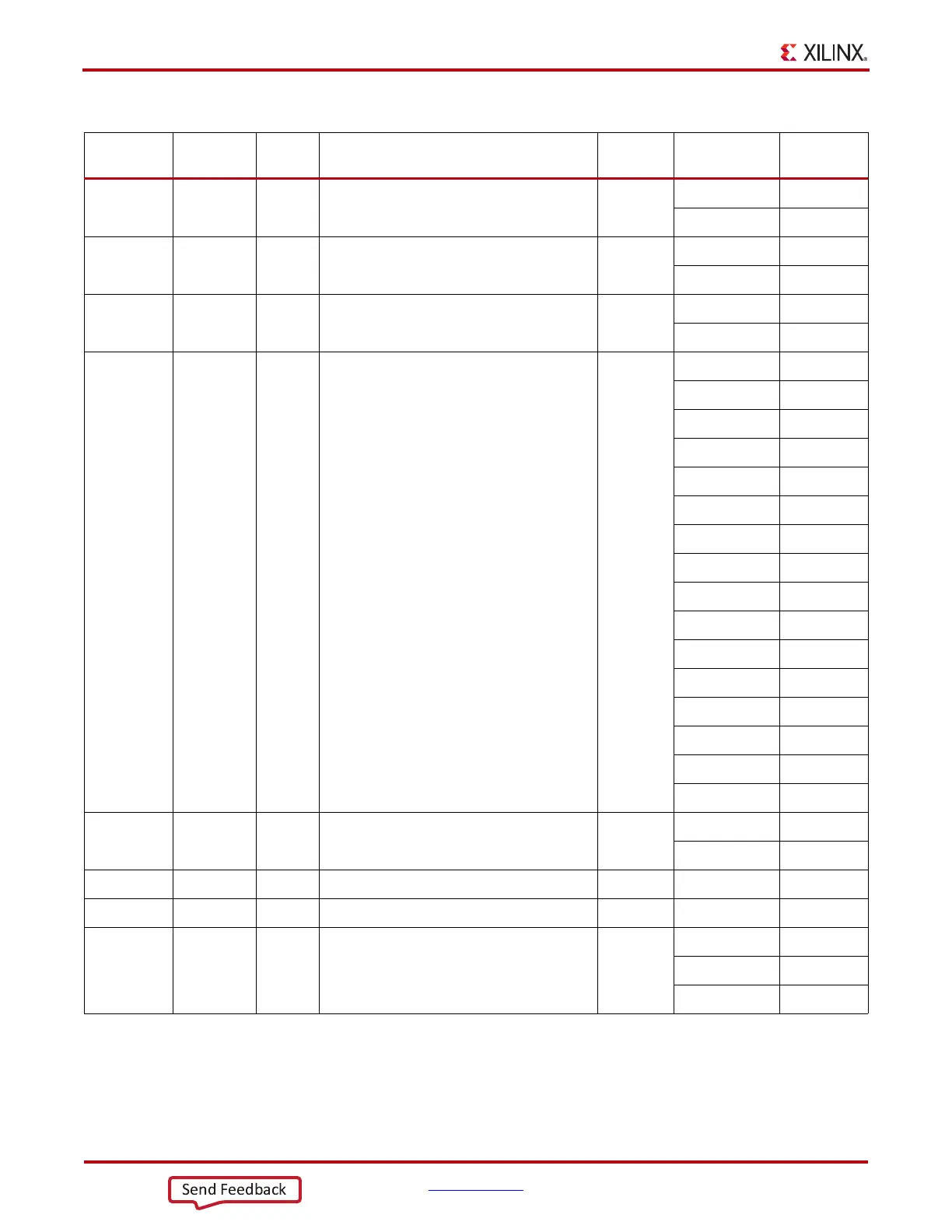

Appendix D: DRP Address Map of the GTP Transceiver

0041 6 R/W ALIGN_MCOMMA_DET 0

FALSE 0

TRUE 1

0041 5 R/W SHOW_REALIGN_COMMA 0

FALSE 0

TRUE 1

0041 4 R/W ALIGN_COMMA_DOUBLE 0

FALSE 0

TRUE 1

0041 3:0 R/W RXSLIDE_AUTO_WAIT 3:0

00

11

22

33

44

55

66

77

88

99

10 10

11 11

12 12

13 13

14 14

15 15

0044 14 R/W CLK_CORRECT_USE 0

FALSE 0

TRUE 1

0044 13:10 R/W CLK_COR_SEQ_1_ENABLE 3:0 0-15 0-15

0044 9:0 R/W CLK_COR_SEQ_1_1 9:0 0-1023 0-1023

0045 15:10 R/W CLK_COR_MAX_LAT 5:0

66

77

88

Table D-2: DRP Map of GTPE2_CHANNEL Primitive (Cont’d)

DRP

Address

DRP Bits R/W Attribute Name

Attribute

Bits

Attribute

Encoding

DRP

Encoding

Loading...

Loading...