296 www.xilinx.com 7 Series FPGAs GTP Transceivers User Guide

UG482 (v1.9) December 19, 2016

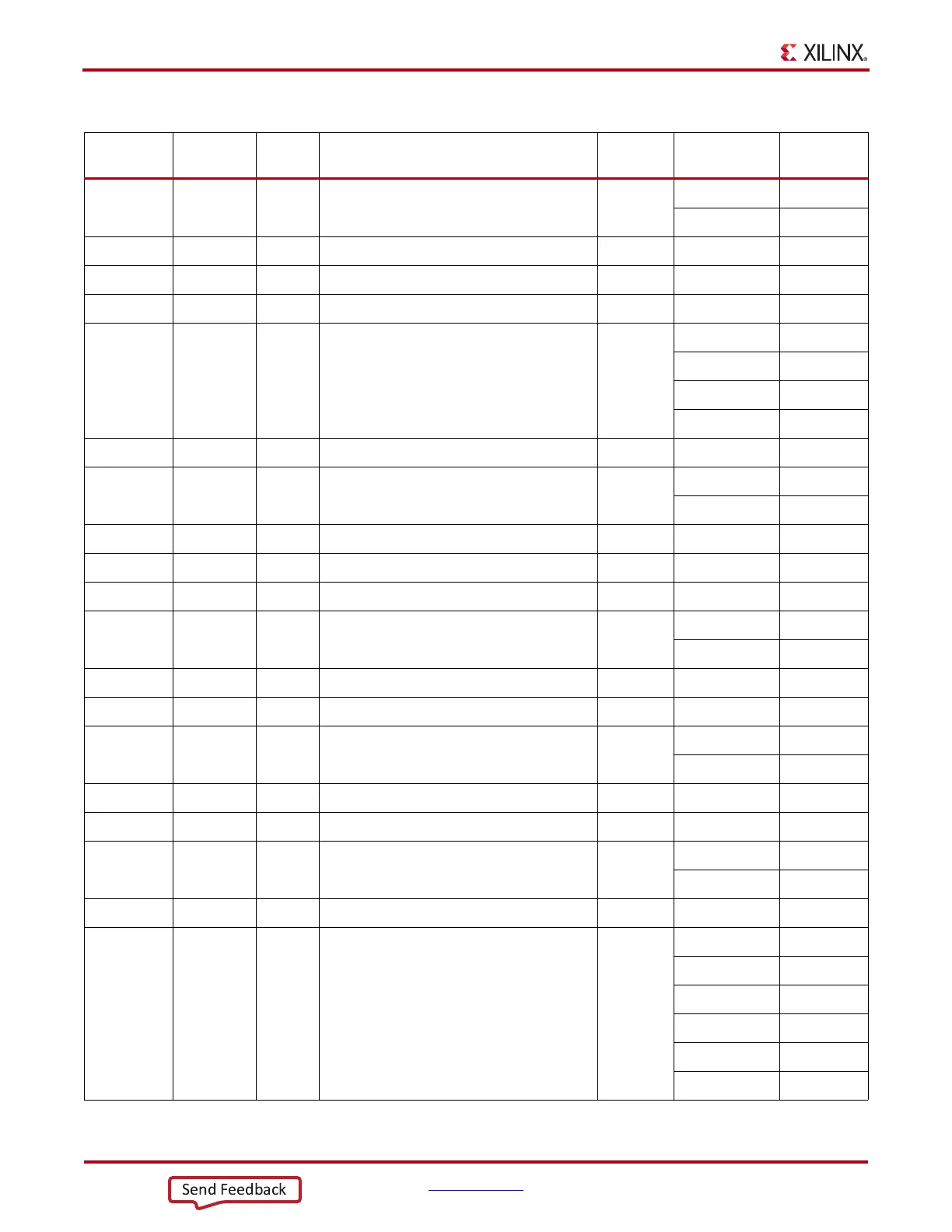

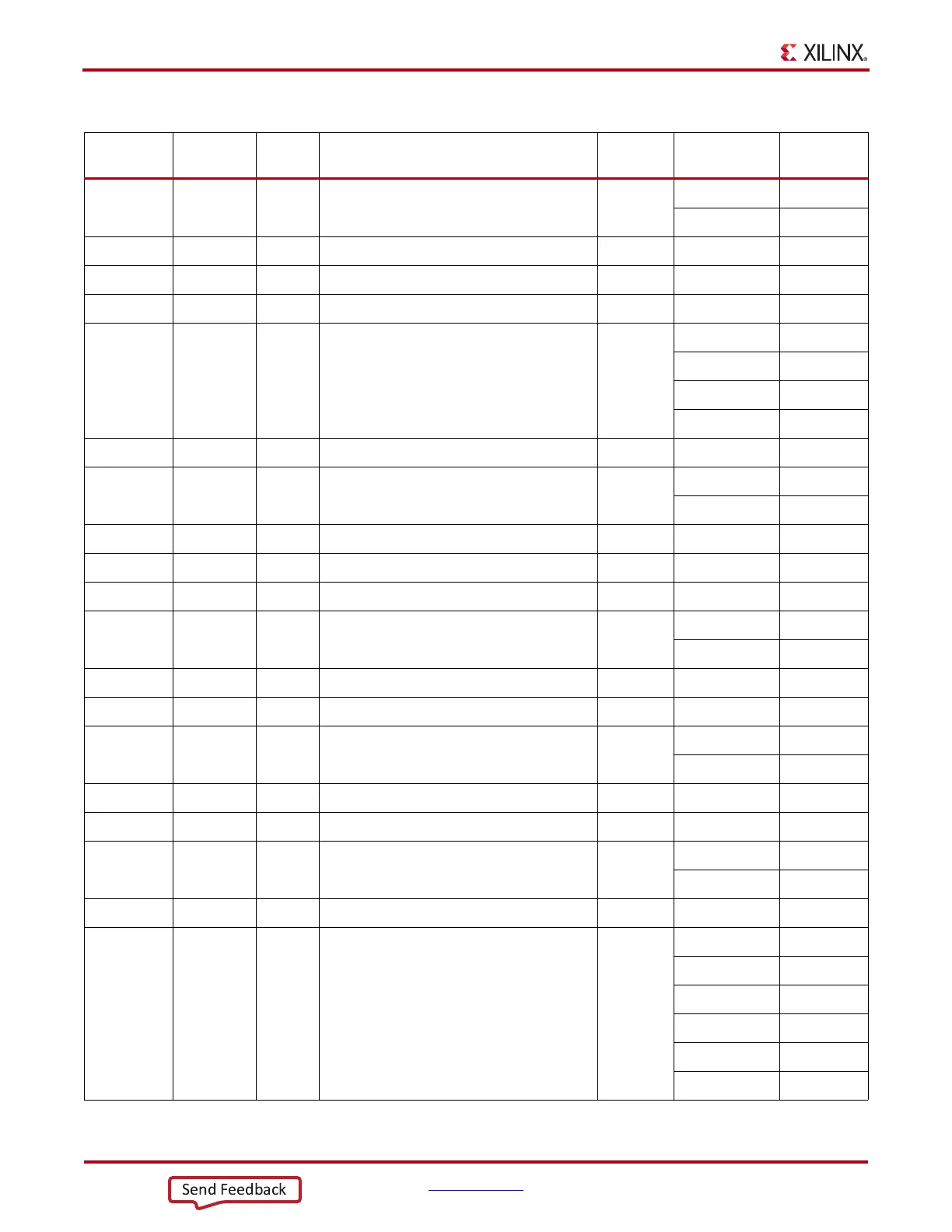

Appendix D: DRP Address Map of the GTP Transceiver

004B 15 R/W RXGEARBOX_EN 0

FALSE 0

TRUE 1

004B 9:0 R/W CLK_COR_SEQ_2_4 9:0 0-1023 0-1023

004C 15:12 R/W CHAN_BOND_SEQ_1_ENABLE 3:0 0-15 0-15

004C 9:0 R/W CHAN_BOND_SEQ_1_1 9:0 0-1023 0-1023

004D 15:14 R/W CHAN_BOND_SEQ_LEN 1:0

10

21

32

43

004D 9:0 R/W CHAN_BOND_SEQ_1_2 9:0 0-1023 0-1023

004E 15 R/W CHAN_BOND_KEEP_ALIGN 0

FALSE 0

TRUE 1

004E 9:0 R/W CHAN_BOND_SEQ_1_3 9:0 0-1023 0-1023

004F 9:0 R/W CHAN_BOND_SEQ_1_4 9:0 0-1023 0-1023

0050 15:12 R/W CHAN_BOND_SEQ_2_ENABLE 3:0 0-15 0-15

0050 11 R/W CHAN_BOND_SEQ_2_USE 0

FALSE 0

TRUE 1

0050 9:0 R/W CHAN_BOND_SEQ_2_1 9:0 0-1023 0-1023

0051 15:12 R/W FTS_LANE_DESKEW_CFG 3:0 0-15 0-15

0051 11 R/W FTS_LANE_DESKEW_EN 0

FALSE 0

TRUE 1

0051 9:0 R/W CHAN_BOND_SEQ_2_2 9:0 0-1023 0-1023

0052 15:12 R/W FTS_DESKEW_SEQ_ENABLE 3:0 0-15 0-15

0052 11 R/W CBCC_DATA_SOURCE_SEL 0

ENCODED 0

DECODED 0

0052 9:0 R/W CHAN_BOND_SEQ_2_3 9:0 0-1023 0-1023

0053 15:12 R/W CHAN_BOND_MAX_SKEW 3:0

11

22

33

44

55

66

Table D-2: DRP Map of GTPE2_CHANNEL Primitive (Cont’d)

DRP

Address

DRP Bits R/W Attribute Name

Attribute

Bits

Attribute

Encoding

DRP

Encoding

Loading...

Loading...