300 www.xilinx.com 7 Series FPGAs GTP Transceivers User Guide

UG482 (v1.9) December 19, 2016

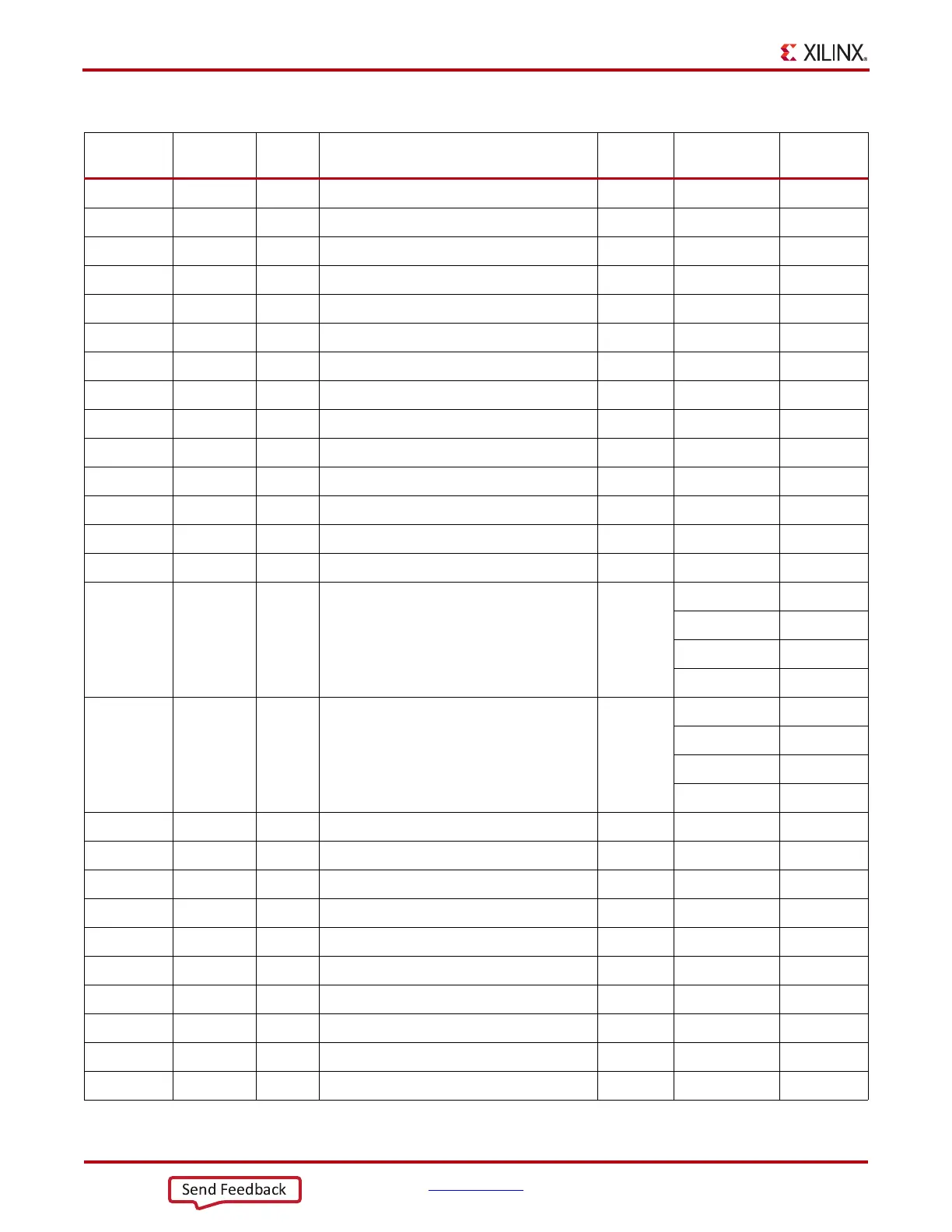

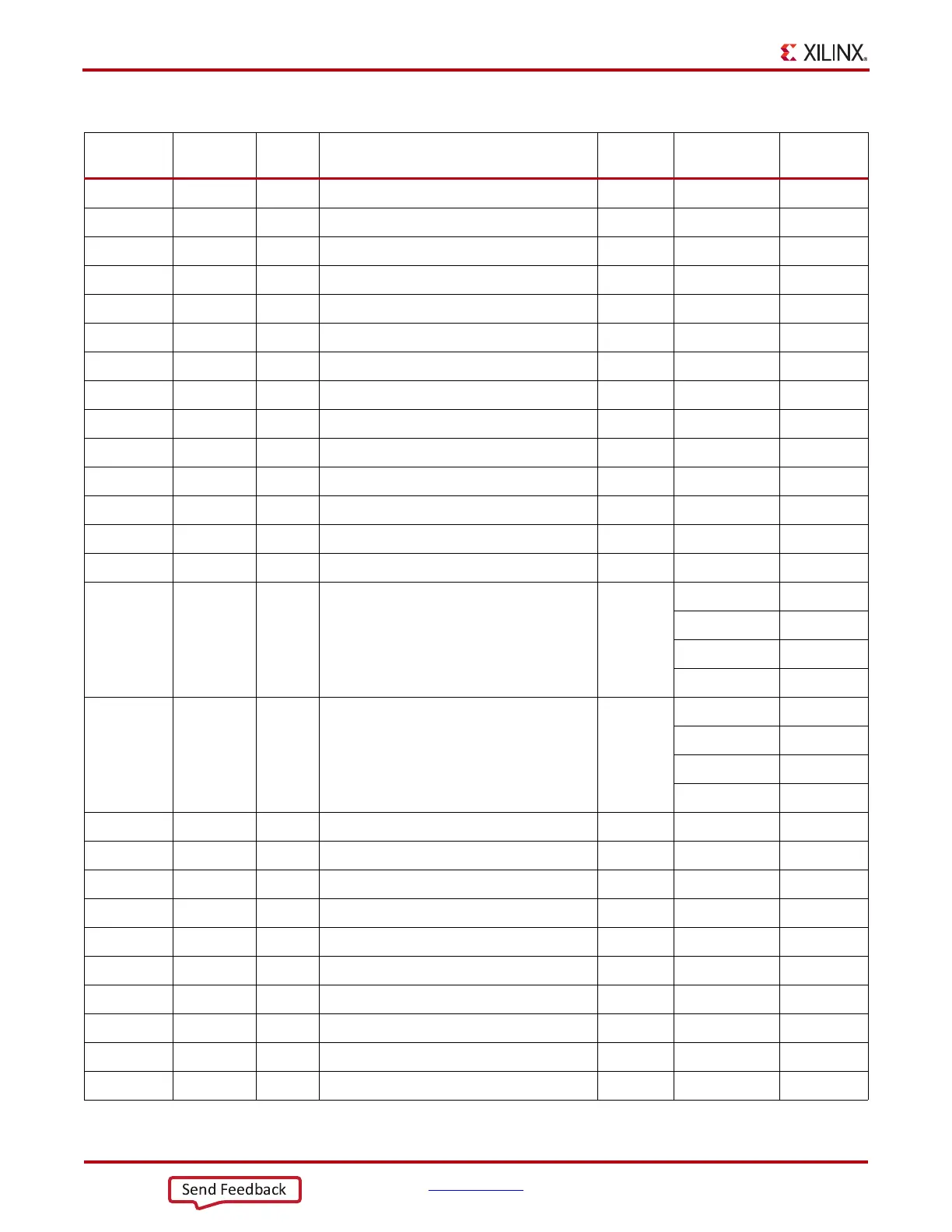

Appendix D: DRP Address Map of the GTP Transceiver

007C 1:0 R/W PMA_RSV3 1:0 0-3 0-3

007D 15 R/W PMA_RSV7 0 0-1 0-1

007D 14 R/W PMA_RSV6 0 0-1 0-1

007D 13:0 R/W TX_RXDETECT_CFG 13:0 0-16383 0-16383

007E 15 R/W CLK_COMMON_SWING 0 0-1 0-1

007E 3:0 R/W RX_CM_TRIM 3:0 0-15 0-15

0081 4 R/W RXLPM_CFG1 0 0-1 0-1

0081 3:0 R/W RXLPM_CFG 3:0 0-15 0-15

0082 15:0 R/W PMA_RSV2 15:0 0-65535 0-65535

0083 15:0 R/W PMA_RSV2 31:16 0-65535 0-65535

0086 15:0 R/W DMONITOR_CFG 15:0 0-65535 0-65535

0087 7:0 R/W DMONITOR_CFG 23:16 0-255 0-255

0088 15 R/W RXLPM_BIAS_STARTUP_DISABLE 0 0-1 0-1

0088 14:11 R/W RXLPM_HF_CFG3 3:0 0-15 0-15

0088 6:4 R/W TXOUT_DIV 2:0

10

21

42

83

0088 2:0 R/W RXOUT_DIV 2:0

10

21

42

83

0089 15:0 R/W CFOK_CFG 15:0 0-65535 0-65535

008A 15:0 R/W CFOK_CFG 31:16 0-65535 0-65535

008B 10:0 R/W CFOK_CFG 42:32 0-2047 0-2047

008C 6:0 R/W CFOK_CFG3 6:0 0-127 0-127

008D 15:13 R/W RXPI_CFG0 2:0 0-7 0-7

008D 12 R/W RXLPM_CM_CFG 0 0-1 0-1

008D 11:10 R/W CFOK_CFG5 1:0 0-3 0-3

008D 9:5 R/W RXLPM_LF_CFG2 4:0 0-31 0-31

008D 4:0 R/W RXLPM_HF_CFG2 4:0 0-31 0-31

008E 15 R/W RXLPM_IPCM_CFG 0 0-1 0-1

Table D-2: DRP Map of GTPE2_CHANNEL Primitive (Cont’d)

DRP

Address

DRP Bits R/W Attribute Name

Attribute

Bits

Attribute

Encoding

DRP

Encoding

Loading...

Loading...