52 www.xilinx.com 7 Series FPGAs GTP Transceivers User Guide

UG482 (v1.9) December 19, 2016

Chapter 2: Shared Features

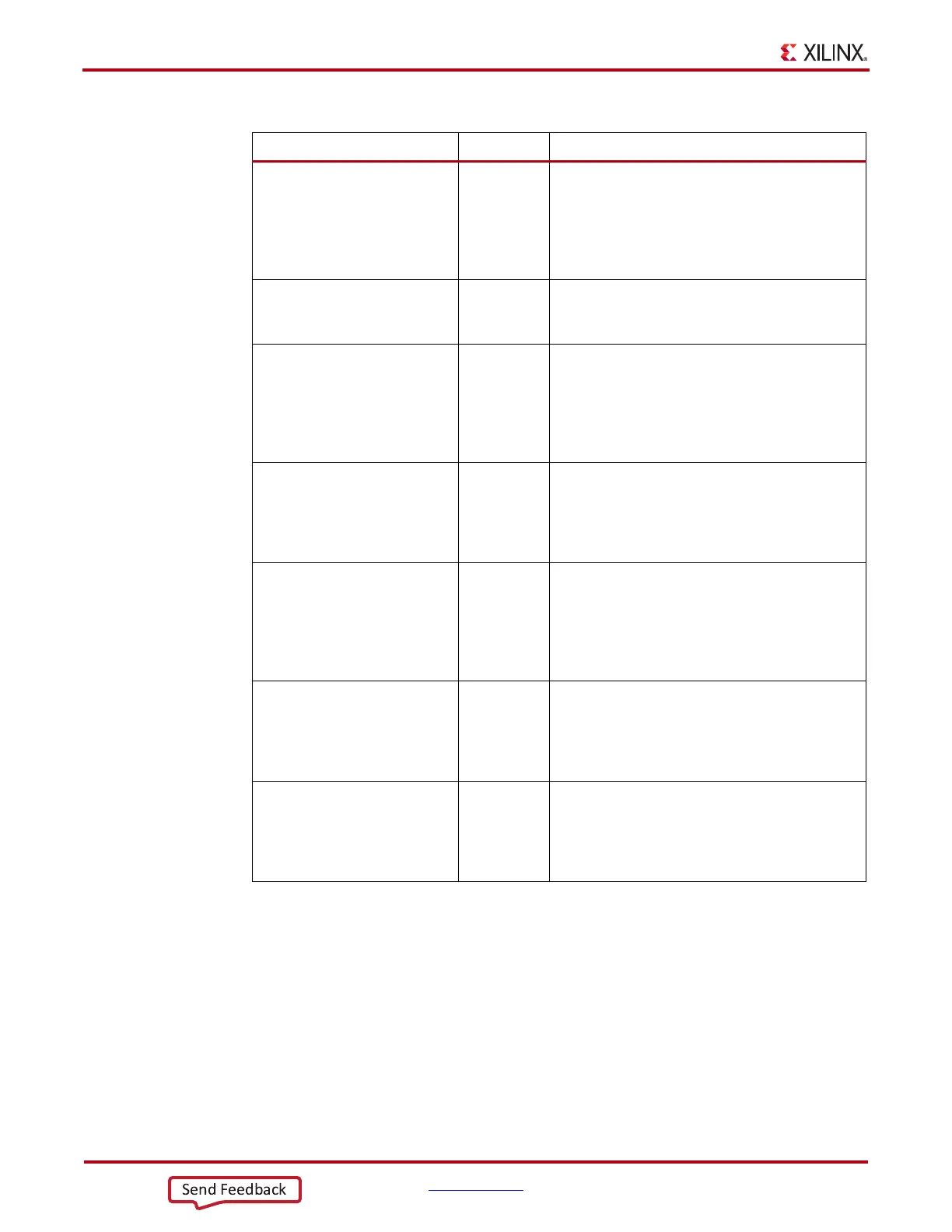

RXPMARESET_TIME 5-bit Binary Reserved. Represents the time duration to apply the

RX PMA reset. The recommended value from the

7 Series FPGAs Transceivers Wizard should be

used. Must be a non-zero value when using

GTRXRESET or RXPMARESET to initiate reset

process.

RXCDRPHRESET_TIME 5-bit Binary Reserved. Represents the time duration to apply RX

CDR Phase reset. Must be a non-zero value when

using RXCDRRESET to initialize the reset process.

RXCDRFREQRESET_TIME 5-bit Binary Reserved. Represents the time duration to apply the

RX CDRFREQ reset. The recommended value

from the 7 Series FPGAs Transceivers Wizard

should be used. Must be a non-zero value when

using RXCDRFREQRESET to initiate the reset

process.

RXLPMRESET_TIME 7-bit Binary Reserved. Represents the time duration to apply the

RX LPM reset. The recommended value from the

7 Series FPGAs Transceivers Wizard should be

used. Must be a non-zero value when using

RXLPMRESET to initiate the reset process.

RXISCANRESET_TIME 5-bit Binary Reserved. Represents the time duration to apply the

RX EYESCAN reset. The recommended value

from the 7 Series FPGAs Transceivers Wizard

should be used. Must be a non-zero value when

using EYESCANRESET_TIME to initiate the reset

process.

RXPCSRESET_TIME 5-bit Binary Reserved. Represents the time duration to apply the

RX PCS reset. The recommended value from the

7 Series FPGAs Transceivers Wizard should be

used. Must be a non-zero value when using

RXPCSRESET to initiate the reset process.

RXBUFRESET_TIME 5-bit Binary Reserved. Represents the time duration to apply the

RX BUFFER reset. The recommended value from

the 7 Series FPGAs Transceivers Wizard should be

used. Must be a non-zero value when using

RXBUFRESET to initiate the reset process.

Table 2-19: RX Initialization and Reset Attributes (Cont’d)

Attribute Type Description

Loading...

Loading...