7 Series FPGAs GTP Transceivers User Guide www.xilinx.com 53

UG482 (v1.9) December 19, 2016

Reset and Initialization

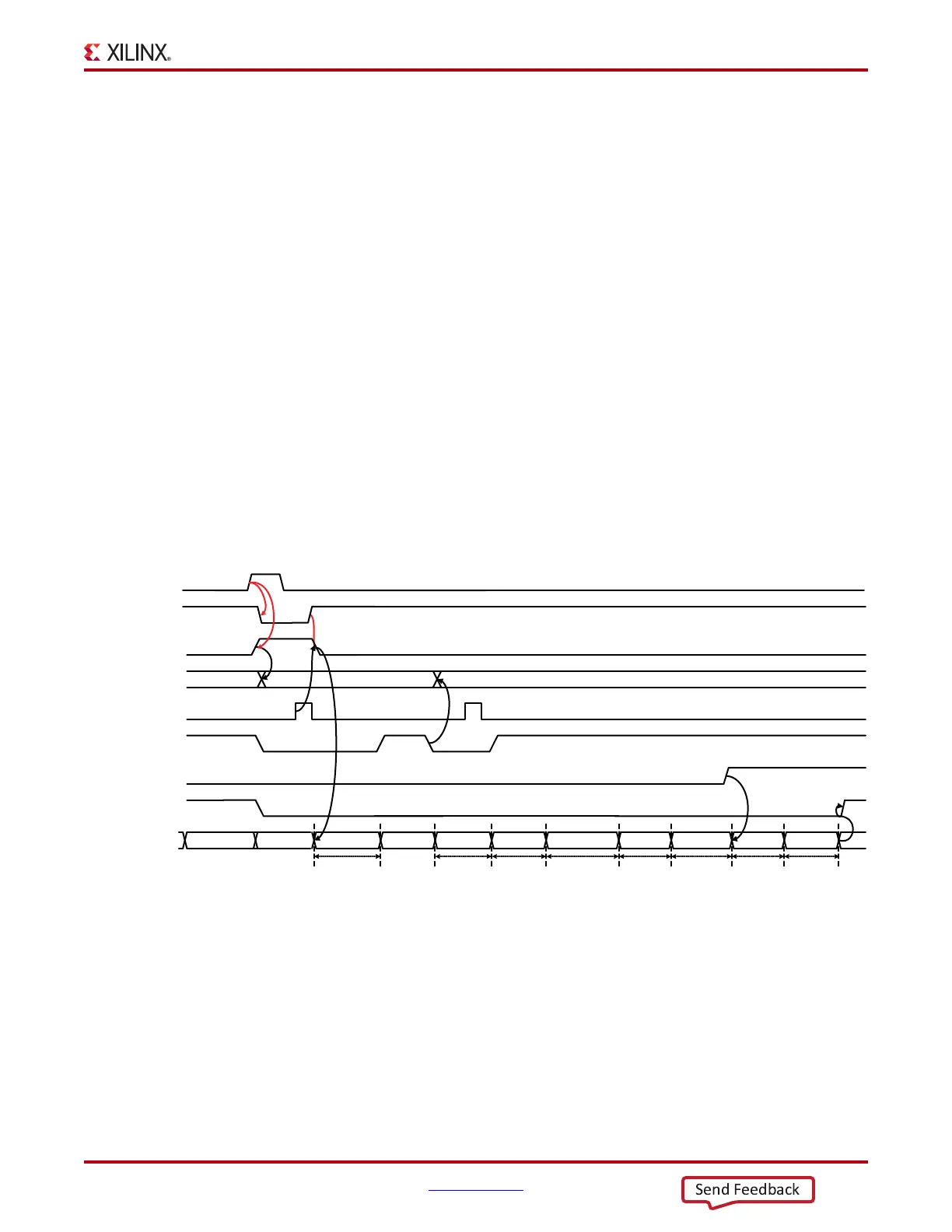

GTP Transceiver RX Reset in Response to Completion of Configuration

The RX reset sequence shown in Figure 2-18 is not automatically started following the global GSR.

These conditions must be met:

1. GTRESETSEL must be driven Low to use the sequential mode.

2. GTRXRESET must be used.

3. All single reset inputs including RXPMARESET, RXCDRRESET, RXCDRFREQRESET,

RXLPMRESET, EYESCANRESET, RXPCSRESET, and RXBUFRESET must be constantly

held Low during the entire reset process before RXRESETDONE goes High.

4. GTRXRESET cannot be driven Low until the associated PLL is locked.

If the reset mode is defaulted to sequential mode upon configuration, then PLL[0/1]RESET and

GTRXRESET can be asserted after waiting for a minimum of 500 ns after configuration is

complete.

If the reset mode is defaulted to single mode, then the user must:

1. Wait a minimum of 500 ns after configuration is complete.

2. Change reset mode to Sequential mode.

3. Wait another 300-500 ns.

When users want to issue an GTRXRESET upon configuration, the steps in Figure 2-19 should be

performed.

Notes relevant to Figure 2-19:

1. “DRP wr” denotes the function of performing a DRP write to addr 9’h011. The exact DRP

transaction is not shown.

2. The sequence of events in Figure 2-19 is not drawn to scale.

3. When the user wants to trigger RX reset upon configuration, assert and release

PLL[0/1]RESET while GTRXRESET is kept asserted. The assertion of GTRXRESET causes

RXPMARESETDONE to go Low.

X-Ref Target - Figure 2-19

Figure 2-19: GTP Transceiver Receiver after FPGA Configuration

UG482_c2_119_021113

IDLE RXPMARESET RXCDRFREQRESET IDLEWAIT RXCDRRESET RXLPMRESET RXISCANRESET RXPCSRESET RXBUFRESETRXOSCALRESET RXOSCALWAIT

restore setting1’b0

RXOSCALRESET

_TIME

RXPMARESET

_TIME

RXPCDRPHRESET

_TIME

RXPCDRFREQRESET

_TIME

RXLPMRESET

_TIME

PLL0RESET/

PLL1RESET

PLL0LOCK/

PLL1LOCK

GTRXRESET

RXUSERRDY

TX RESET FSM

RXRESETDONE

RXPMARESETDONE

DRPRDY

DRP

(wr addr ‘h011, bit[11])

RXISCANRESET

_TIME

RXPCSRESET

_TIME

RXBUFRESET

_TIME

Loading...

Loading...