7 Series FPGAs GTP Transceivers User Guide www.xilinx.com 49

UG482 (v1.9) December 19, 2016

Reset and Initialization

Ports and Attributes

Table 2-18 lists the ports required by the GTP transceiver‘s RX initialization process.

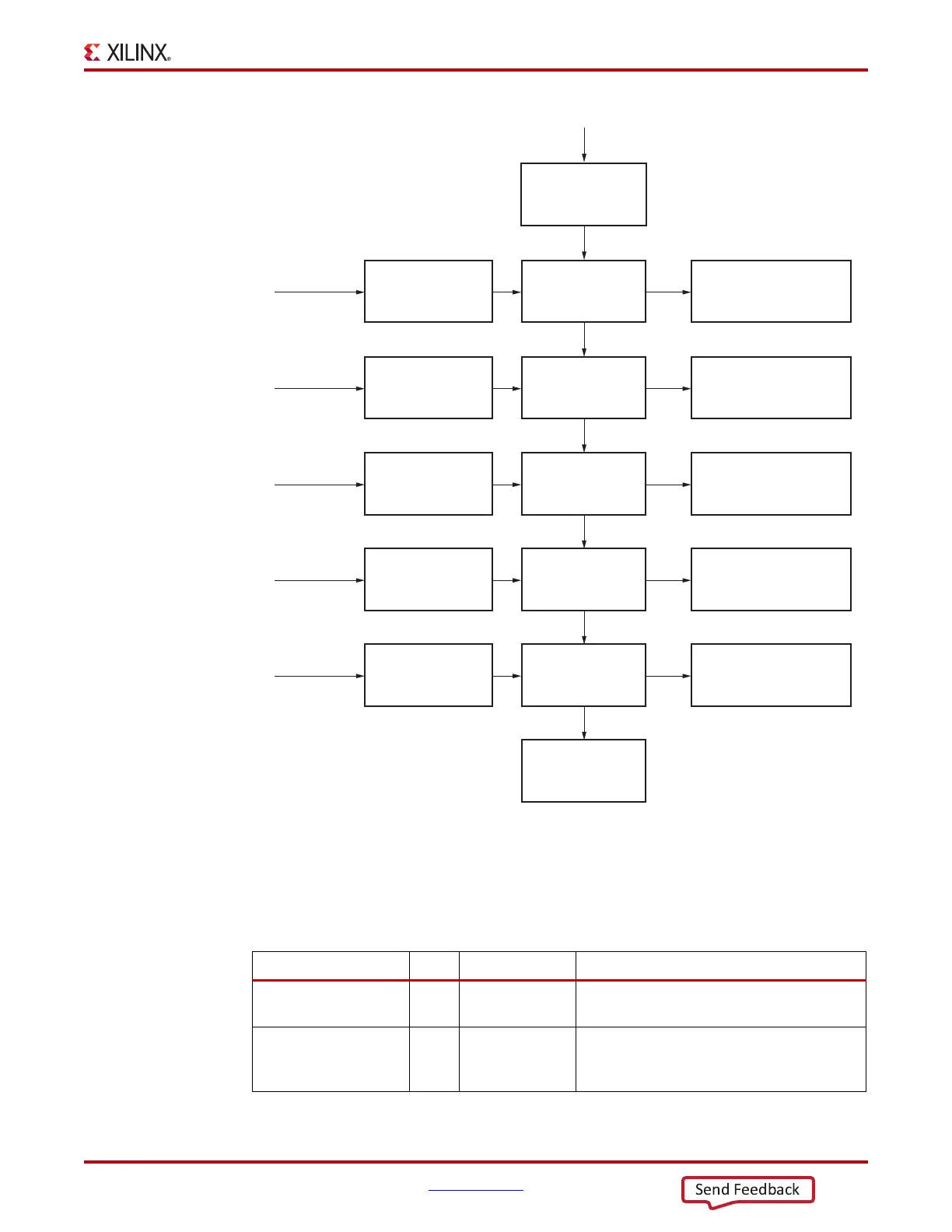

X-Ref Target - Figure 2-18

Figure 2-18: GTP Transceiver RX Reset State Machine Sequence

WAIT until

RXPMARESET

from High to Low

RXPMARESET

Process

WAIT until

GTRXRESET

from High to Low

RXPMARESET Done

when

RXRESETDONE High

RXPMARESET

High

GTRXRESET

High

Single

Mode

WAIT until

RXLPMRESET

from High to Low

RXLPMRESET

Process

RXLPMRESET

Done when

RXRESETDONE High

RXLPMRESET

High

Single

Mode

WAIT until

EYESCANRESET

from High to Low

EYESCANRESET

Process

EYESCANRESET

Done when

RXRESETDONE High

EYESCANRESET

High

Single

Mode

WAIT until

RXPCSRESET

from High to Low

RXPCSRESET

Process

RXPCSRESET Done

when

RXRESETDONE High

RXPCSRESET

High

Single

Mode

WAIT until

RXBUFRESET

from High to Low

RXBUFRESET

Process

RXRESETDONE

High

RXBUFRESET Done

when

RXRESETDONE High

RXBUFRESET

High

Single

Mode

Sequence Mode & RXUSERRDY

UG482_c2_118_021113

Table 2-18: RX Initialization and Reset Ports

Port Dir Clock Domain Description

GTRXRESET In Async This port is driven High and then deasserted to

start the full Channel RX reset sequence.

RXOSCALRESET In Async Reserved. The recommended value from the 7

Series FPGAs Transceivers Wizard should be

used.

Loading...

Loading...