50 www.xilinx.com 7 Series FPGAs GTP Transceivers User Guide

UG482 (v1.9) December 19, 2016

Chapter 2: Shared Features

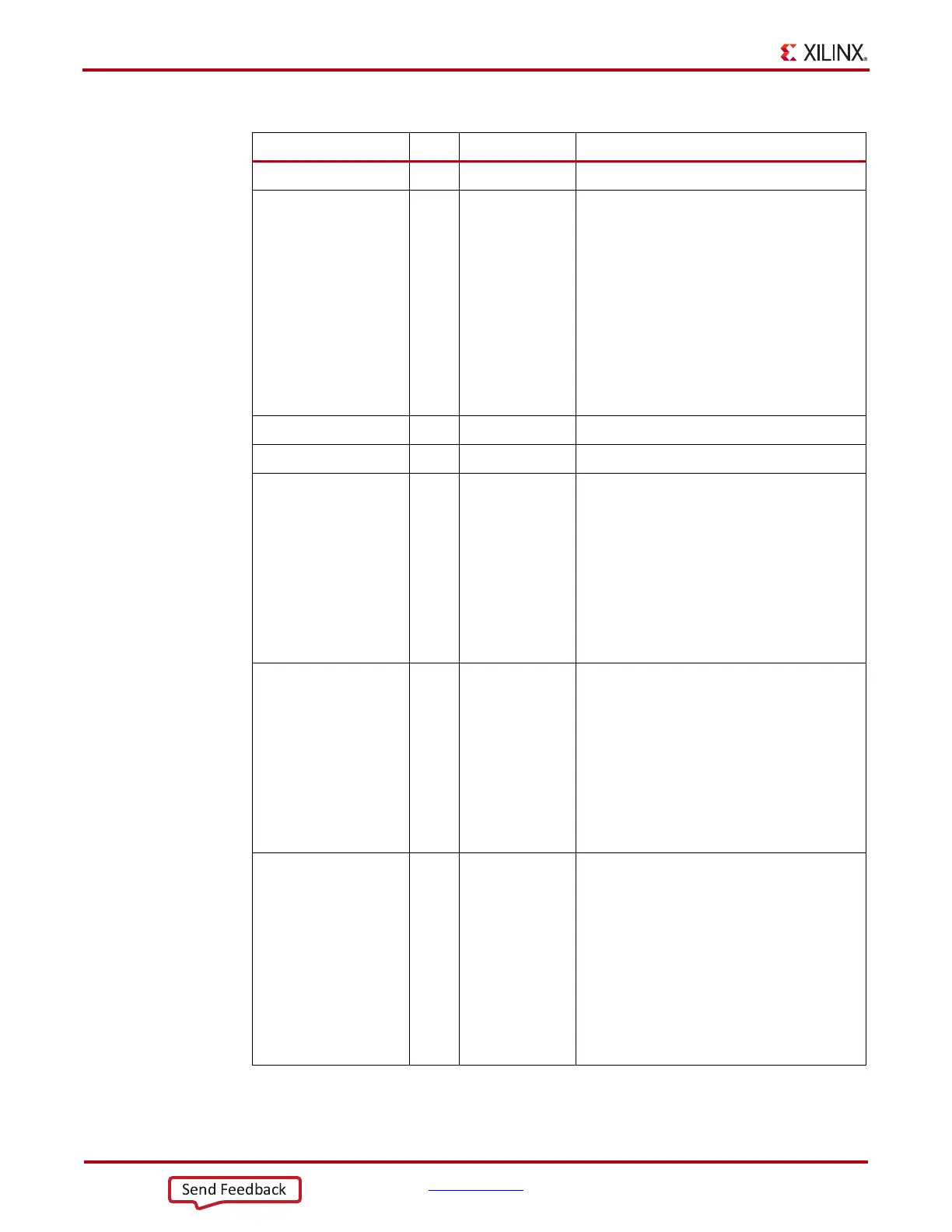

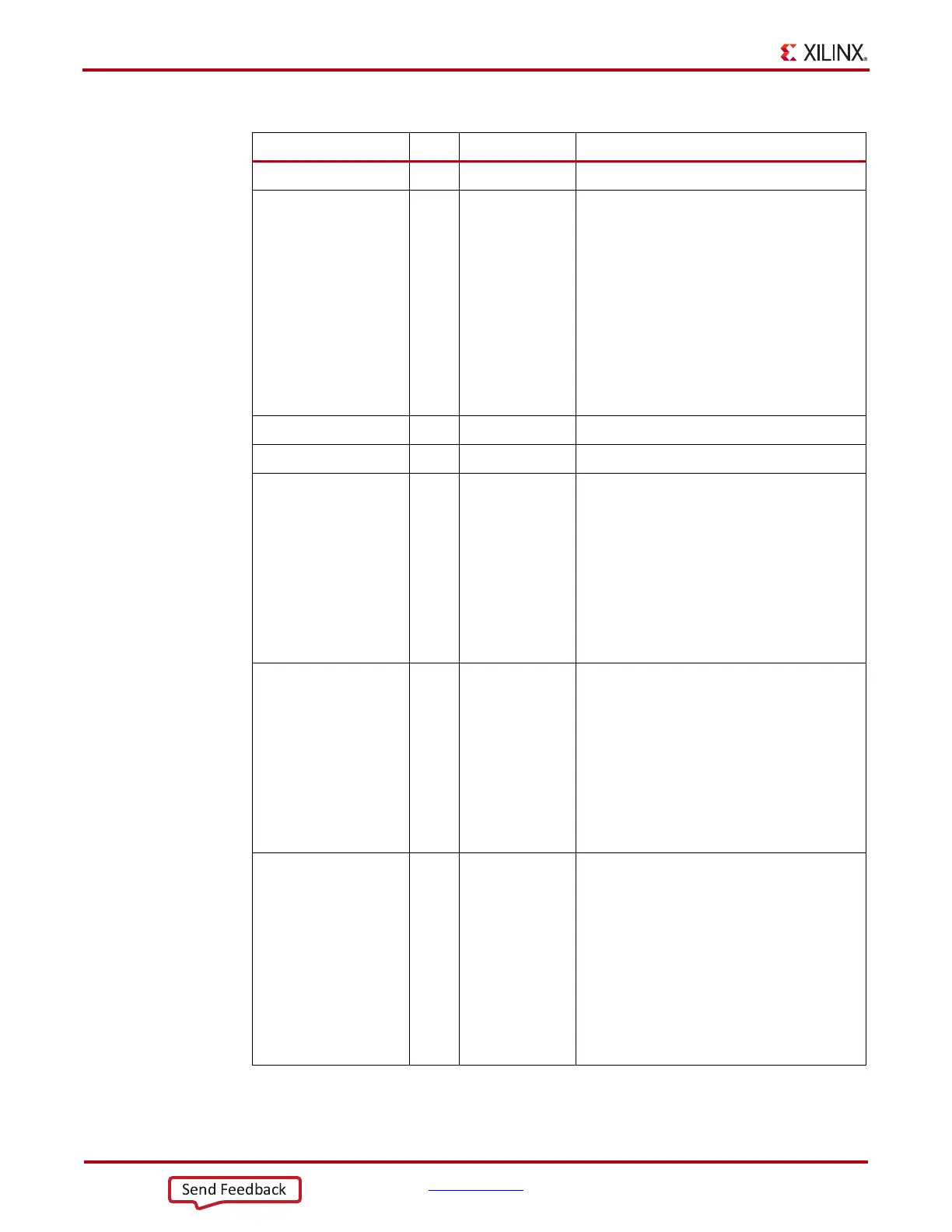

RXOSINTDONE Out Async Reserved.

RXPMARESET In Async This port is driven High and then deasserted to

start RX PMA reset process. In single mode,

activating RXPMARESET resets only the RX

PMA blocks not including CDR and LPM. In

sequential mode, activating RXPMARESET

starts the RX reset process as shown in

Figure 2-18 from RXPMARESET and

followed by RXCDRPHASERESET,

RXCDRFREQRESET, RXLPMRESET,

EYESCANRESET, RXPCSRESET, and

RXBUFRESET. Detailed coverage on

sequential mode is listed in Table 2-20.

RXCDRRESET In Async Reserved. Tied Low.

RXCDRFREQRESET In Async Reserved. Tied Low.

RXLPMRESET In Async This port is driven High and then deasserted to

start the LPM reset process. In single mode,

activating RXLPMRESET resets only the RX

LPM circuits. In sequential mode, activating

RXLPMRESET starts the RX reset process as

shown in Figure 2-18 from RXLPMRESET

and followed by EYESCANRESET,

RXPCSRESET, and RXBUFRESET. Detailed

coverage in sequential mode is listed in

Table 2-20.

EYESCANRESET In Async This port is driven High and then deasserted to

start the EYESCAN reset process. In single

mode, activating EYESCANRESET resets

only the RX Eye Scan circuits. In sequential

mode, activating EYESCANRESET starts the

RX reset process as shown in Figure 2-18 from

EYESCANRESET and followed by

RXPCSRESET, and RXBUFRESET. Detailed

coverage in sequential mode is listed in

Table 2-20.

RXPCSRESET In Async This port is driven High and then deasserted to

start the PCS reset process. In single mode,

activating RXPCSRESET resets only the RX

PCS circuits. In sequential mode, activating

RXPCSRESET starts the RX reset process as

shown in Figure 2-18 from RXPCSRESET and

followed by RXBUFRESET. Detailed

coverage in sequential mode is listed in

Table 2-20.

In both modes, RXPCSRESET does not start

the reset process until RXUSERRDY is High.

Table 2-18: RX Initialization and Reset Ports (Cont’d)

Port Dir Clock Domain Description

Loading...

Loading...