7 Series FPGAs GTP Transceivers User Guide www.xilinx.com 59

UG482 (v1.9) December 19, 2016

Reset and Initialization

After Power-up and Configuration

The entire GTP RX requires a reset after configuration. See GTP Transceiver RX Reset in Response

to Completion of Configuration for procedure.

After Turning on a Reference Clock to the PLL Being Used

If the reference clock(s) changes or GTP transceiver(s) are powered up after configuration,

GTRXRESET should be toggled after the PLL fully completes its reset procedure.

After Changing the Reference Clock to the PLL Being Used

Whenever the reference clock input to the PLL is changed, the PLL must be reset afterwards to

ensure that it locks to the new frequency. The GTRXRESET should be toggled after the PLL fully

completes its reset procedure.

After Assertion/Deassertion of PLL[0/1]PD, for the PLL Being Used

When the PLL being used goes back to normal operation after power down, the PLL must be reset.

The GTRXRESET should be toggled after the PLL fully completes its reset procedure.

After Assertion/Deassertion of RXPD[1:0]

After the RXPD signal is deasserted, GTRXRESET must be toggled.

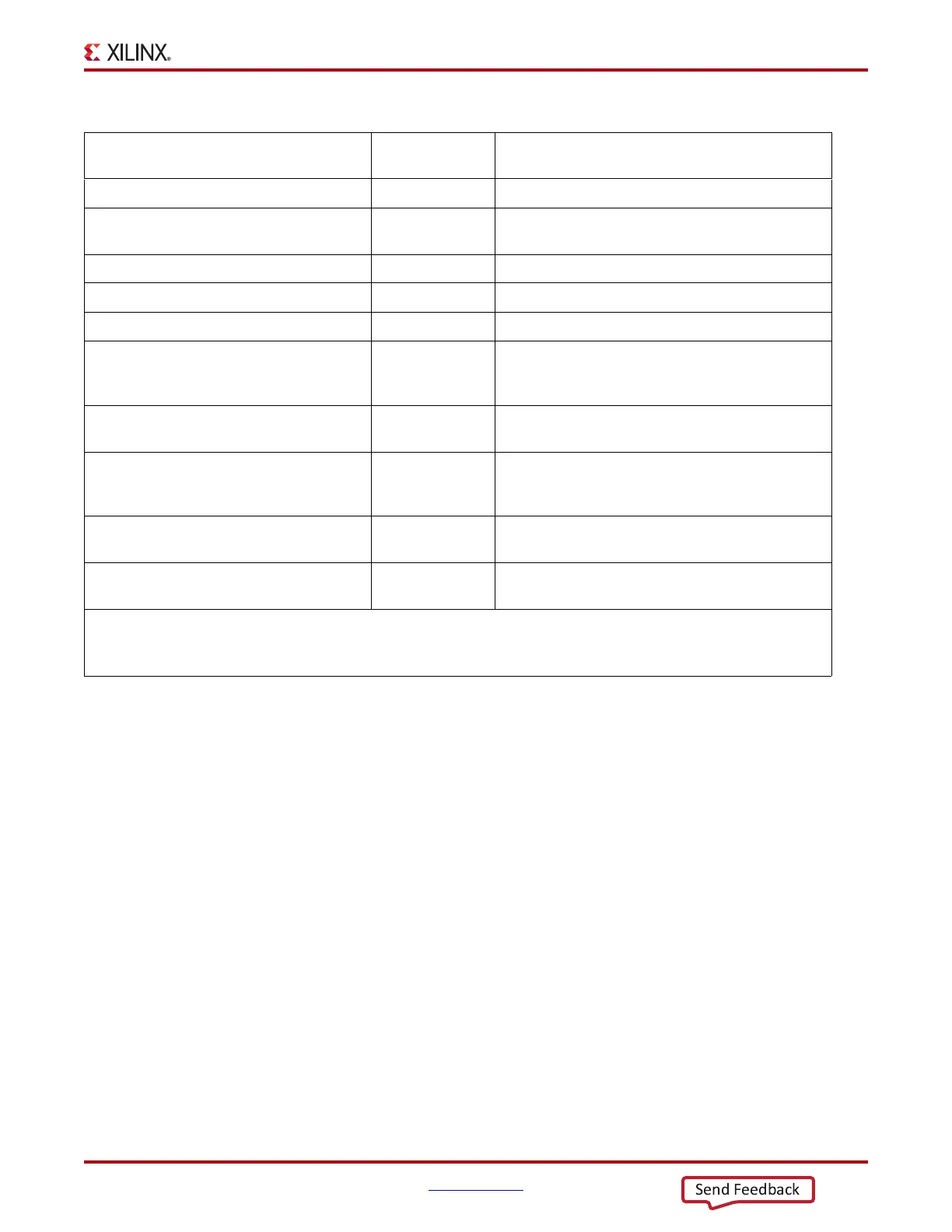

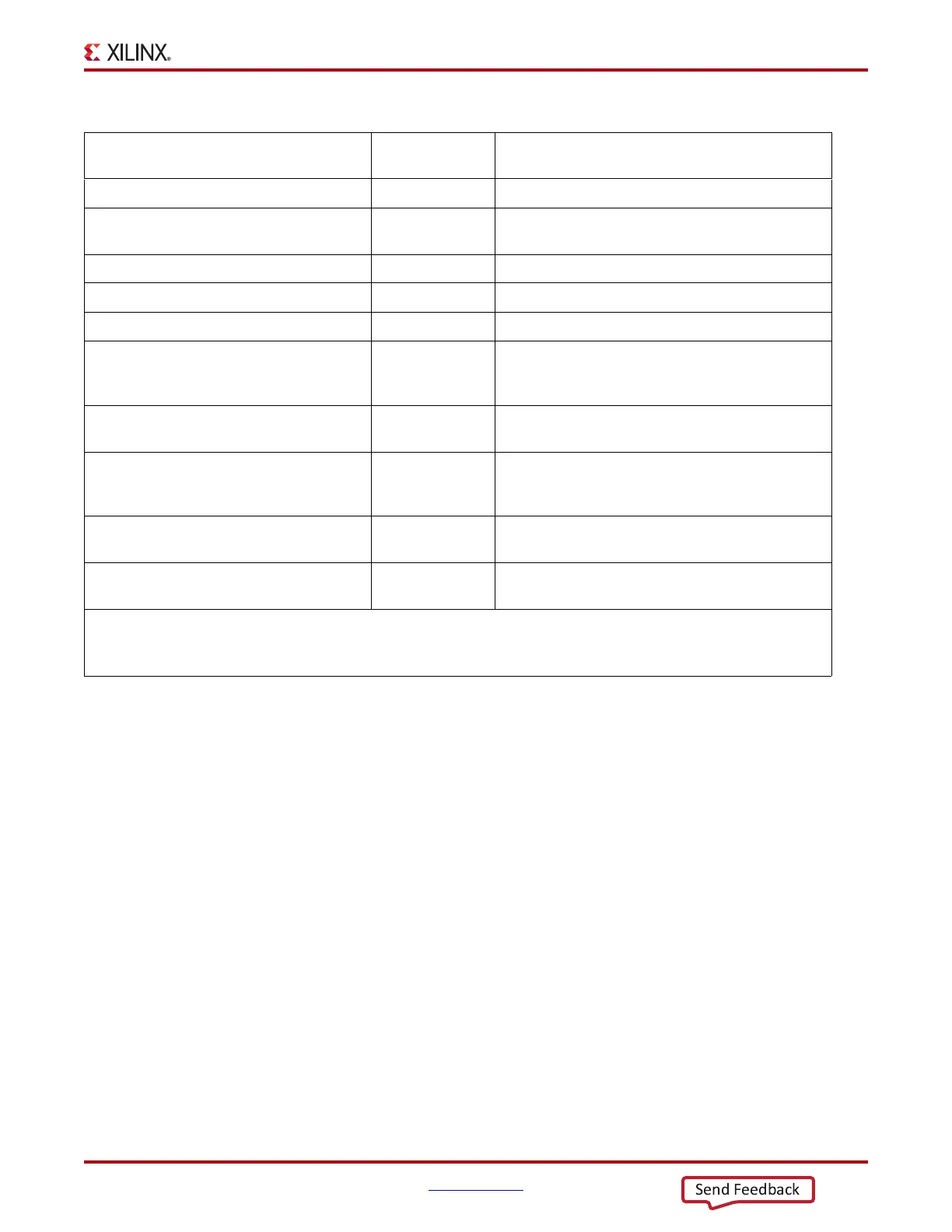

After remote power up Entire RX GTRXRESET

Electrical idle Entire RX Handled automatically with appropriate attribute

settings

After connecting RXN/RXP

(2)

Entire RX GTRXRESET

After recovered clock becomes stable RX Elastic Buffer RXBUFRESET

After an RXBUFFER error RX Elastic Buffer RXBUFRESET

After changing channel bonding mode on the

fly

RX Elastic Buffer RX elastic buffer is reset automatically after change in

channel bonding mode by setting

RXBUF_RESET_ON_CB_CHANGE to TRUE

After PRBS error PRBS Error

Counter

PRBSCNTRESET

After comma realignment RX Elastic Buffer

(optional)

RX elastic buffer is reset automatically after comma

realignment by setting

RXBUF_RESET_ON_COMMAALIGN to TRUE

After entering or exiting Far-End PMA

loopback

Entire TX GTTXRESET

After entering or exiting Near-End PMA

loopback

Entire RX GTRXRESET

Notes:

1. The recommended reset has the smallest impact on the other components of the GTP transceiver.

2. It is assumed that RXN/RXP are connected simultaneously.

Table 2-22: Recommended Resets for Common Situations (Cont’d)

Situation

Components to

be Reset

Recommended Reset

(1)

Loading...

Loading...