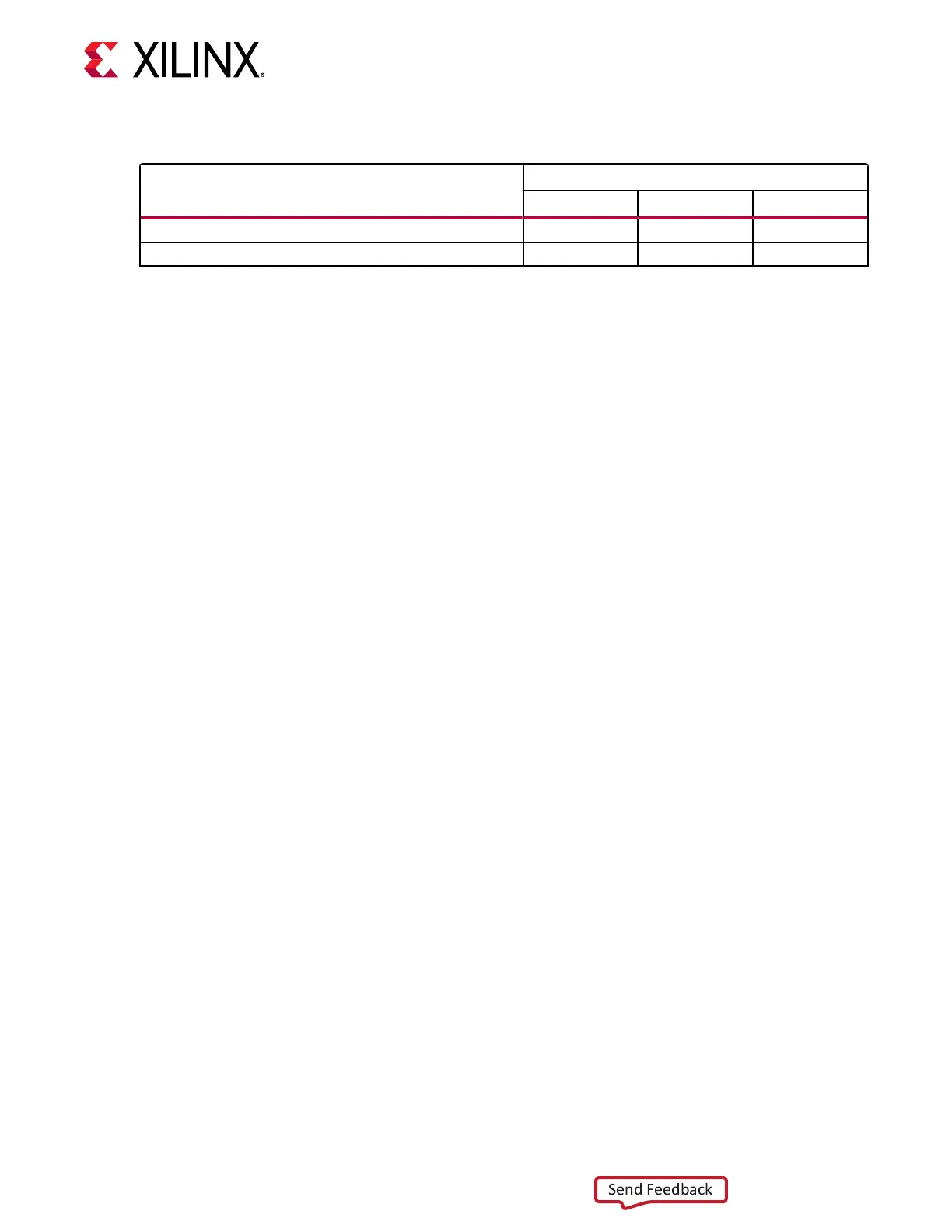

Table 68: Valid RS-FEC Operating Sub-Modes

Control Signal

Sub-Modes

1 2 3

FEC_RXn_BYPASS_INDICATION 0 0 1

FEC_RXn_BYPASS_CORRECTION 0 1 0

Sub-mode 1: Full Operation

In this sub-mode, the RS-FEC engine detects and corrects errors. If a codeword with up to 15

symbol errors is received, the errors are corrected. If a codeword with 16 or more symbol errors

is received, the erroneous data is agged soon aer the start of data output.

Sub-mode 2: Error Indication, No Error Correction

In this sub-mode, the RS-FEC engine detects errors but does not correct them. If a codeword

with one or more errors is received, no error correcon is aempted, but the erroneous data is

agged soon aer the start of data output.

Sub-mode 3: Error Correction, No Error Indication

In this sub-mode, the RS-FEC engine detects and corrects errors. If a codeword with up to 15

symbol errors is received, the errors are corrected. If a codeword with 16 or more symbol errors

is received, no correcon is possible, and the erroneous data is not agged unl aer it has been

output.

Usage Model

When FEC is enabled in 50G mode, bit 0 of each RXDATA bus is the rst bit received in me,

and bit 159 is the last bit received in me. The RXDATASTART signal is driven High whenever

the RXDATA for the associated slice contains the rst 160 bits of a codeword. Output

codewords are always aligned so that bit 0 of a codeword is on bit 0 of the RXDATA bus.

When FEC is enabled in 100G mode, bit 0 of CH0_RXDATA is the rst bit received in me, and

bit 159 of CH1_RXDATA is the last bit received in me. The CH0_RXDATASTART signal is driven

High whenever the RXDATA buses contain the rst 320 bits of a codeword. Output codewords

are always aligned so that bit 0 of a codeword is on bit 0 of CH0_RXDATA. CH0_RXDATASTART

should be ignored in 100G mode.

The RXDATAISAM signal is driven High alongside RXDATASTART whenever the codeword

received on the associated slice contains an alignment marker. This signal is not acve when the

FEC is congured in 50G raw mode. In 100G mode, CH1_RXDATAISAM should be ignored.

Chapter 4: Receiver

UG581 (v1.0) January 4, 2019 www.xilinx.com

Virtex UltraScale+ GTM Transceivers 111

Loading...

Loading...