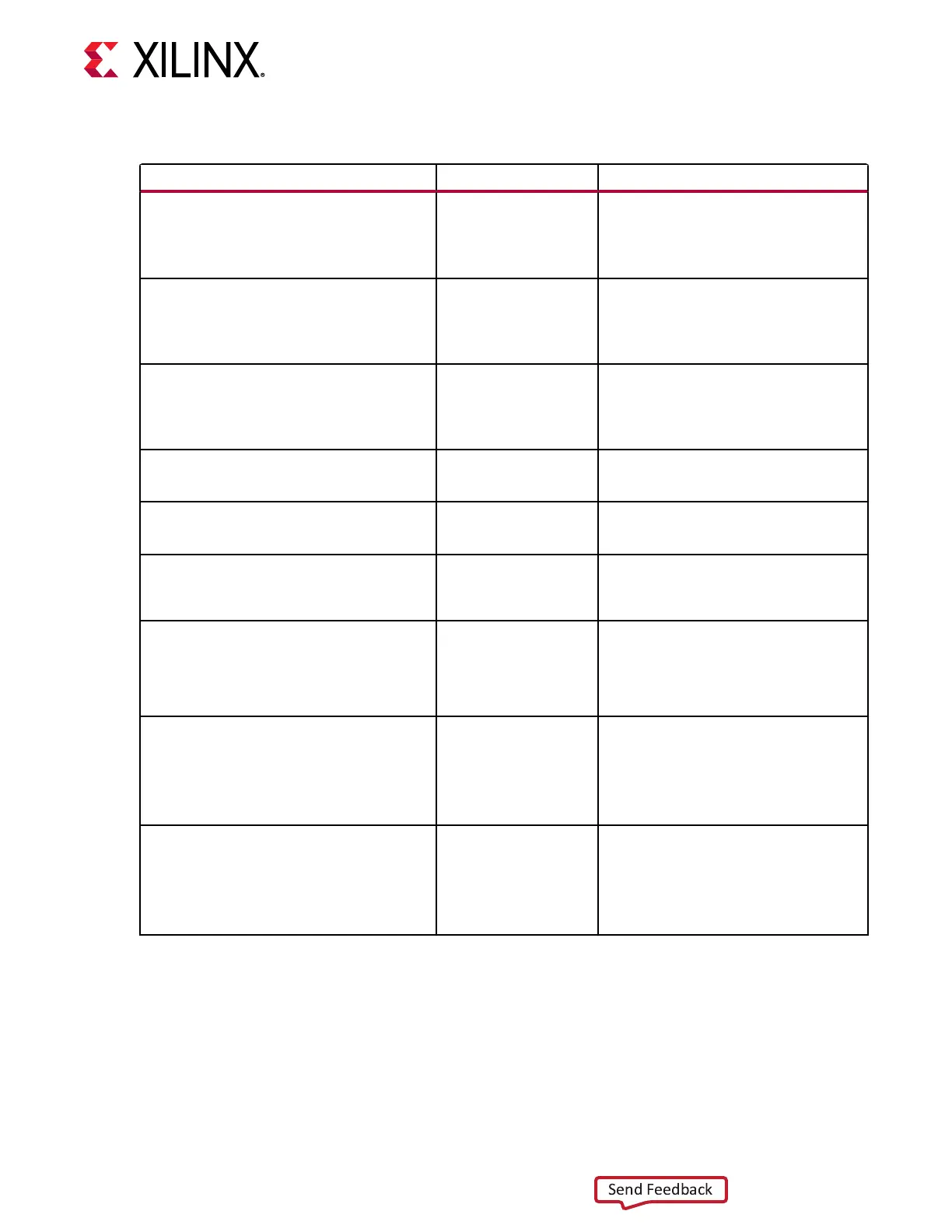

Table 67: RX FEC Attributes (cont'd)

Attribute Type Description

FEC_RX1_BYPASS_CORRECTION [1] FEC RX slice 1 error correction select:

1’b0: Error correct enabled.

1’b1: Error correct disabled.

FEC_RX0_BYPASS_INDICATION [2] FEC RX slice 0 error indicator enable:

1’b0: Error indicator enabled.

1’b1: Error indicator disabled.

FEC_RX1_BYPASS_INDICATION [3] FEC RX slice 1 error indicator enable:

1’b0: Error indicator enabled.

1’b1: Error indicator disabled.

FEC_CFG1[15:0] (FEC_RX0_VL_LENGTH[15:0])

FEC_CFG3[4] (FEC_RX0_VL_LENGTH[16])

17-bit Binary Frame length (in 66-bit blocks per PCS lane)

for FEC RX slice 0. Ignored if FEC RX slice 0 is

configured in raw FEC mode.

FEC_CFG2[15:0] (FEC_RX1_VL_LENGTH[15:0])

FEC_CFG3[5] (FEC_RX1_VL_LENGTH[16])

17-bit Binary Frame length (in 66-bit blocks per PCS lane)

for FEC RX slice 1. Ignored if FEC RX slice 1 is

configured in raw FEC mode.

FEC_CFG4[15:0] (FEC_RX_VL_MARKER_ID0[15:0])

FEC_CFG5[15:0] (FEC_RX_VL_MARKER_ID0[31:16])

FEC_CFG6[15:0] (FEC_RX_VL_MARKER_ID0[47:32])

FEC_CFG7[15:0] (FEC_RX_VL_MARKER_ID0[63:48])

64-bit Binary Alignment marker 0 (common), for 50GE

operation on FEC RX slice 0, and for 100GE,

FlexO, and Interlaken operation on FEC RX

slices 0–1.

FEC_CFG8[15:0] (FEC_RX_VL_MARKER_ID1[15:0])

FEC_CFG9[15:0] (FEC_RX_VL_MARKER_ID1[31:16])

FEC_CFG10[15:0]

(FEC_RX_VL_MARKER_ID1[47:32])

FEC_CFG11[15:0]

(FEC_RX_VL_MARKER_ID1[63:48])

64-bit Binary

Alignment marker 0 (common) for 50GE

operation on FEC RX slice 1. Ignored if FEC

RX slice 0 is configured in 100G mode.

FEC_CFG12[15:0] (FEC_RX_VL_MARKER_ID4[15:0])

FEC_CFG13[15:0]

(FEC_RX_VL_MARKER_ID4[31:16])

FEC_CFG14[15:0]

(FEC_RX_VL_MARKER_ID4[47:32])

FEC_CFG15[15:0]

(FEC_RX_VL_MARKER_ID4[63:48])

64-bit Binary

Alignment marker 4 (lane-specific) for

100GE, FlexO, and Interlaken operation on

FEC RX slice 0–1. Alignment marker 2 (lane-

specific) for 50GE operation on FEC RX slice

0.

FEC_CFG16[15:0] (FEC_RX_VL_MARKER_ID5[15:0])

FEC_CFG17[15:0]

(FEC_RX_VL_MARKER_ID5[31:16])

FEC_CFG18[15:0]

(FEC_RX_VL_MARKER_ID5[47:32])

FEC_CFG19[15:0]

(FEC_RX_VL_MARKER_ID5[63:48])

64-bit Binary

Alignment marker 5 (lane-specific) for

100GE, FlexO, and Interlaken operation on

FEC RX slice 0–1.

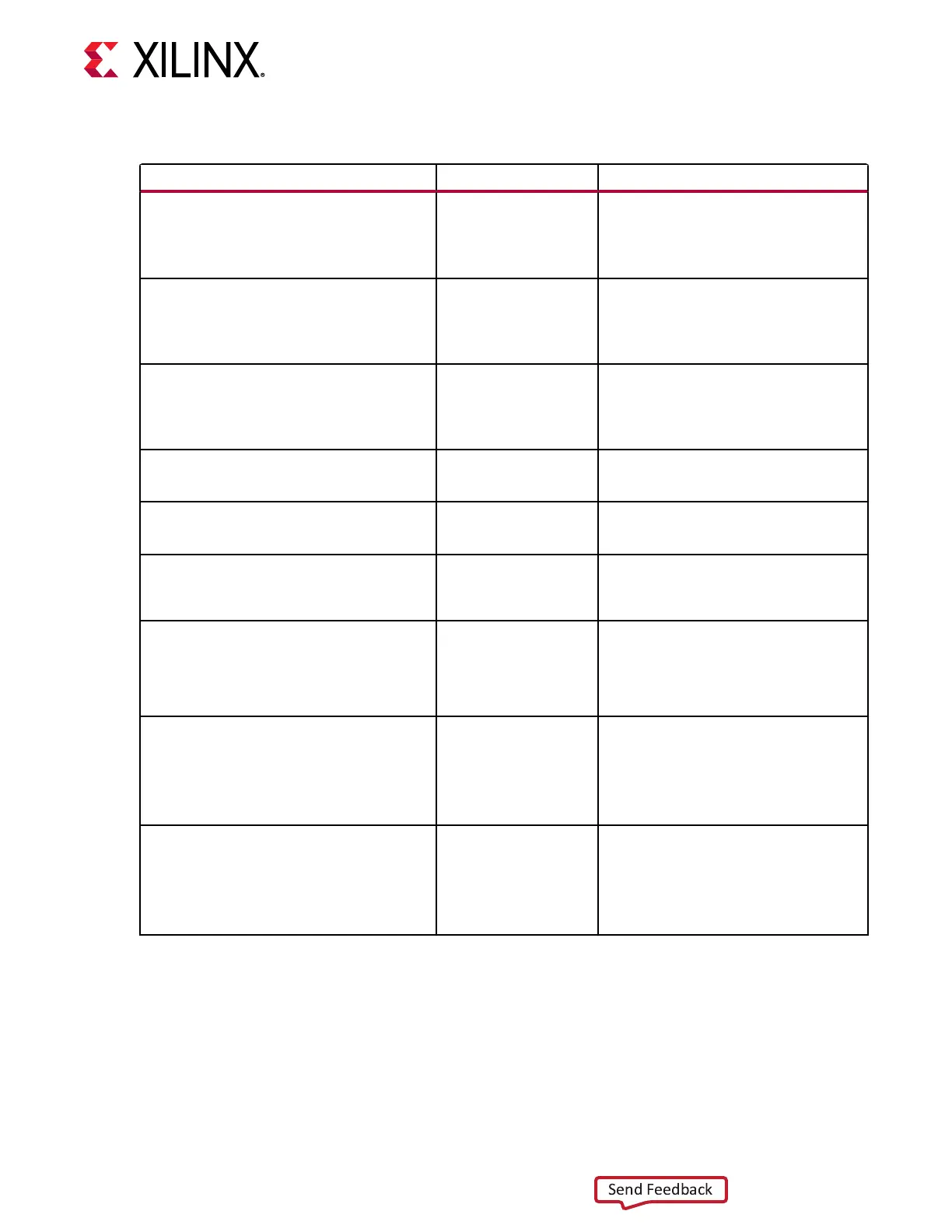

RS-FEC Sub-Modes

There are three sub-modes of RS-FEC decoder operaon dened by the IEEE 802.3bj

specicaon. The primary purpose of the dierent sub-modes is to allow latency to be reduced

in cases where the line BER is low enough that full error correcon is not required. The following

table lists the valid RS-FEC operang sub-modes. When congured in 2x50G FEC mode, the sub-

mode can be set independently for each slice.

Chapter 4: Receiver

UG581 (v1.0) January 4, 2019 www.xilinx.com

Virtex UltraScale+ GTM Transceivers 110

Loading...

Loading...