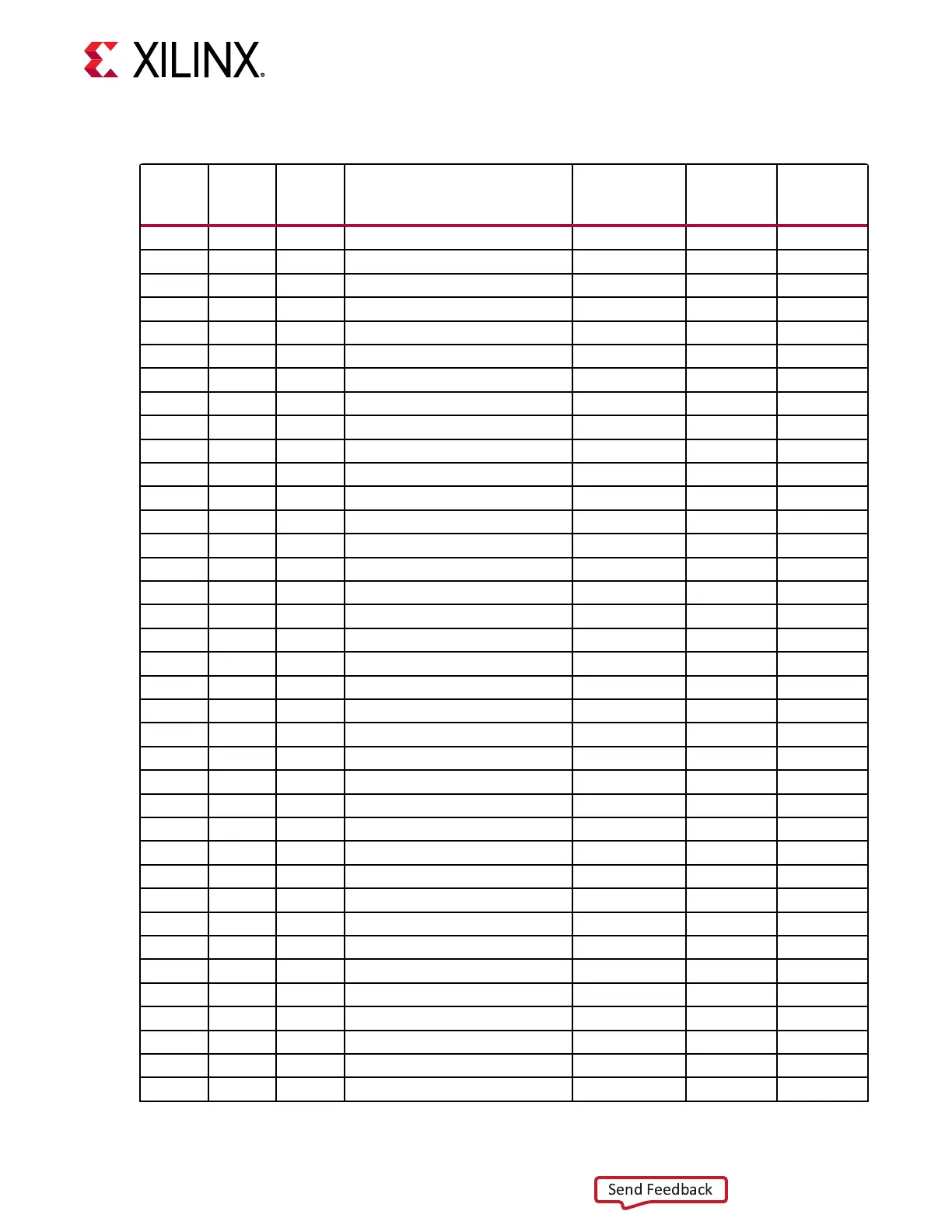

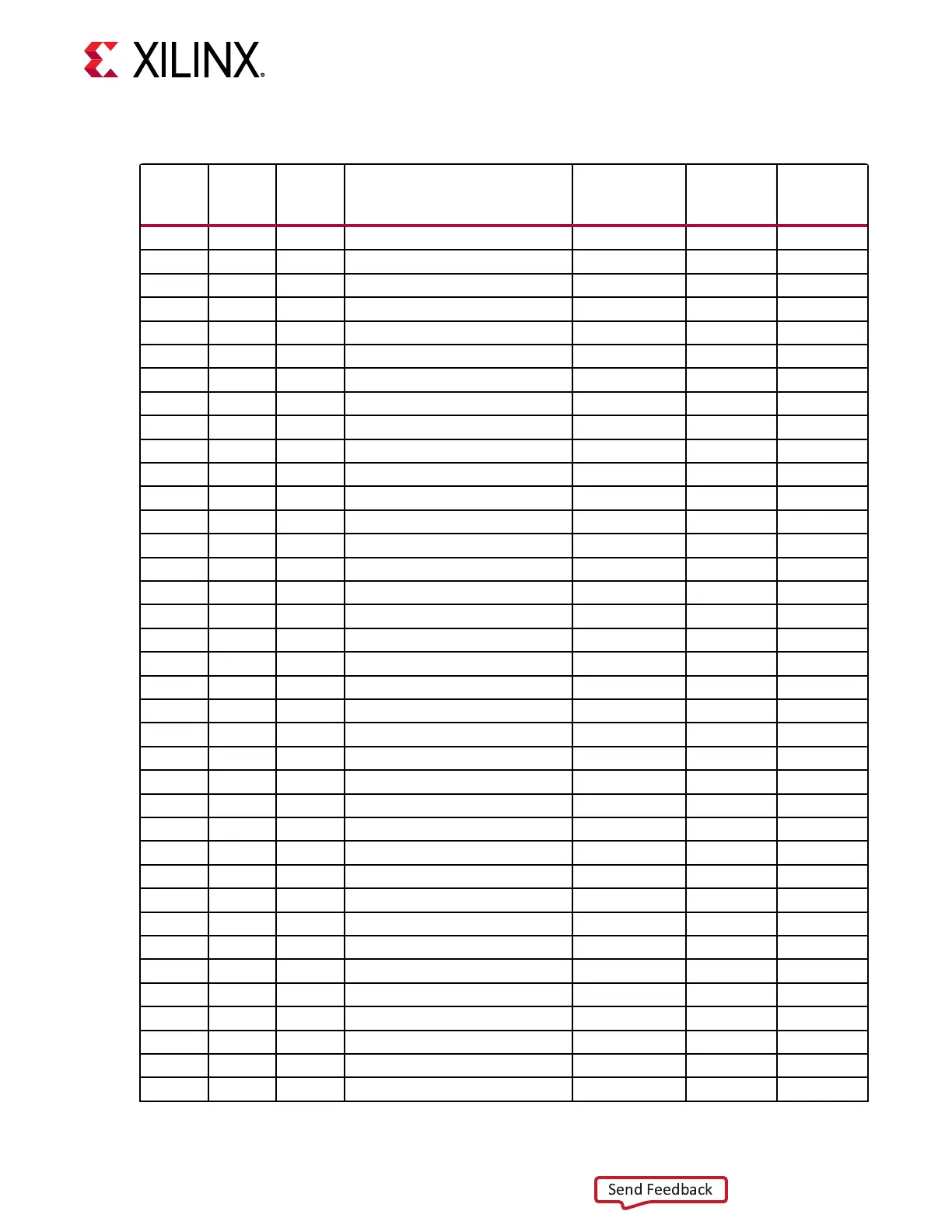

Table 75: DRP Map of GTM_DUAL Primitive (cont'd)

DRP

Addres

s

DRP

Bits

R/W Attribute Name Attribute Bits

Attribute

Encoding

DRP

Encoding

0x099 [15:0] R/W CH0_A_CH_CFG4 [15:0] 0–65535 0–65535

0x09a [15:0] R/W CH0_A_CH_CFG5 [15:0] 0–65535 0–65535

0x09b [15:0] R/W CH0_A_CH_CFG6 [15:0] 0–65535 0–65535

0x0a0 [15:0] R/W CH0_RST_TIME_CFG0 [15:0] 0–65535 0–65535

0x0a1 [15:0] R/W CH0_RST_TIME_CFG1 [15:0] 0–65535 0–65535

0x0a2 [15:0] R/W CH0_RST_TIME_CFG2 [15:0] 0–65535 0–65535

0x0a3 [15:0] R/W CH0_RST_TIME_CFG3 [15:0] 0–65535 0–65535

0x0a4 [15:0] R/W CH0_RST_TIME_CFG4 [15:0] 0–65535 0–65535

0x0a5 [15:0] R/W CH0_RST_TIME_CFG5 [15:0] 0–65535 0–65535

0x0a6 [15:0] R/W CH0_RST_TIME_CFG6 [15:0] 0–65535 0–65535

0x0a7 [15:0] R/W CH0_RST_LP_ID_CFG0 [15:0] 0–65535 0–65535

0x0a8 [15:0] R/W CH0_RST_LP_ID_CFG1 [15:0] 0–65535 0–65535

0x0a9 [15:0] R/W CH0_RST_LP_CFG0 [15:0] 0–65535 0–65535

0x0aa [15:0] R/W CH0_RST_LP_CFG1 [15:0] 0–65535 0–65535

0x0ab [15:0] R/W CH0_RST_LP_CFG2 [15:0] 0–65535 0–65535

0x0ac [15:0] R/W CH0_RST_LP_CFG3 [15:0] 0–65535 0–65535

0x0ad [15:0] R/W CH0_RST_LP_CFG4 [15:0] 0–65535 0–65535

0x0ae [15:0] R/W RST_CFG [15:0] 0–65535 0–65535

0x0af [15:0] R/W RST_PLL_CFG0 [15:0] 0–65535 0–65535

0x0b0 [15:0] R/W PLL_CFG0 [15:0] 0–65535 0–65535

0x0b1 [15:0] R/W PLL_CFG1 [15:0] 0–65535 0–65535

0x0b2 [15:0] R/W PLL_CFG2 [15:0] 0–65535 0–65535

0x0b3 [15:0] R/W PLL_CFG3 [15:0] 0–65535 0–65535

0x0b4 [15:0] R/W PLL_CFG4 [15:0] 0–65535 0–65535

0x0b5 [15:0] R/W PLL_CFG5 [15:0] 0–65535 0–65535

0x0b6 [15:0] R/W PLL_CFG6 [15:0] 0–65535 0–65535

0x0b7 [15:0] R/W SDM_SEED_CFG0 [15:0] 0–65535 0–65535

0x0b8 [15:0] R/W SDM_SEED_CFG1 [15:0] 0–65535 0–65535

0x0b9 [15:0] R/W SDM_CFG0 [15:0] 0–65535 0–65535

0x0ba [15:0] R/W SDM_CFG1 [15:0] 0–65535 0–65535

0x0bb [15:0] R/W SDM_CFG2 [15:0] 0–65535 0–65535

0x0bc [15:0] R/W A_SDM_DATA_CFG0 [15:0] 0–65535 0–65535

0x0bd [15:0] R/W A_SDM_DATA_CFG1 [15:0] 0–65535 0–65535

0x0be [15:0] R/W PLL_CRS_CTRL_CFG0 [15:0] 0–65535 0–65535

0x0bf [15:0] R/W PLL_CRS_CTRL_CFG1 [15:0] 0–65535 0–65535

0x0c0 [15:0] R/W A_CFG [15:0] 0–65535 0–65535

0x0c1 [15:0] R/W SAP_CFG0 [15:0] 0–65535 0–65535

Appendix A: DRP Address Map of the GTM Transceiver in UltraScale+ FGPAs

UG581 (v1.0) January 4, 2019 www.xilinx.com

Virtex UltraScale+ GTM Transceivers 137

Loading...

Loading...