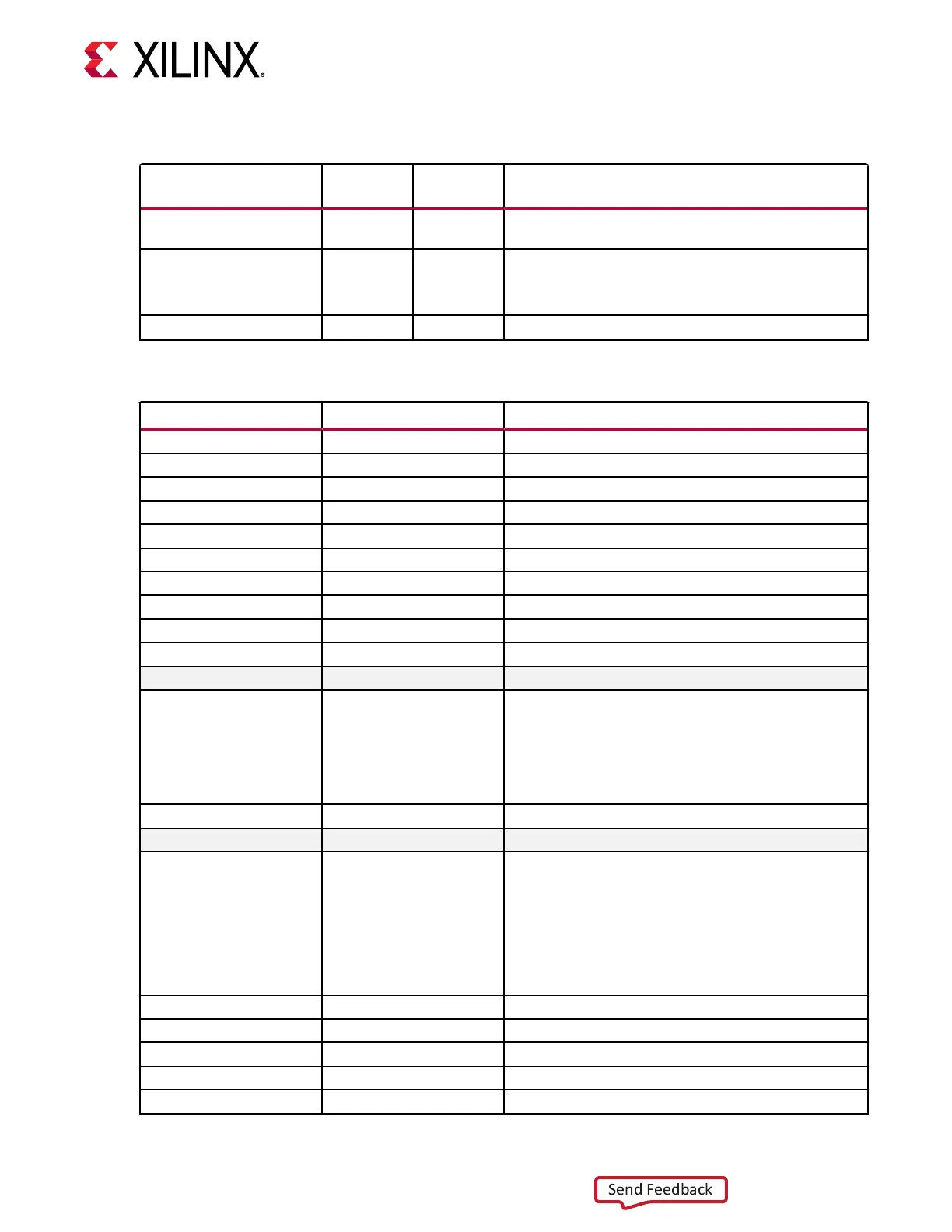

Table 9: LCPLL Ports (cont'd)

Port Direction

Clock

Domain

Description

RCALEN In Async Reserved. This port must be set to 1’b1. Do not modify this

value.

SDMDATA[25:0] In Async Input to set the Fractional Divider. Bits [SDMWIDTH +

1:SDMWIDTH] are the integer part of the divider in two’s

complement. Bits [SDMWIDTH – 1:SDMWIDTH] set the

fractional part of the divider.

SDMTOGGLE In Async Reserved. Set to 1’b0.

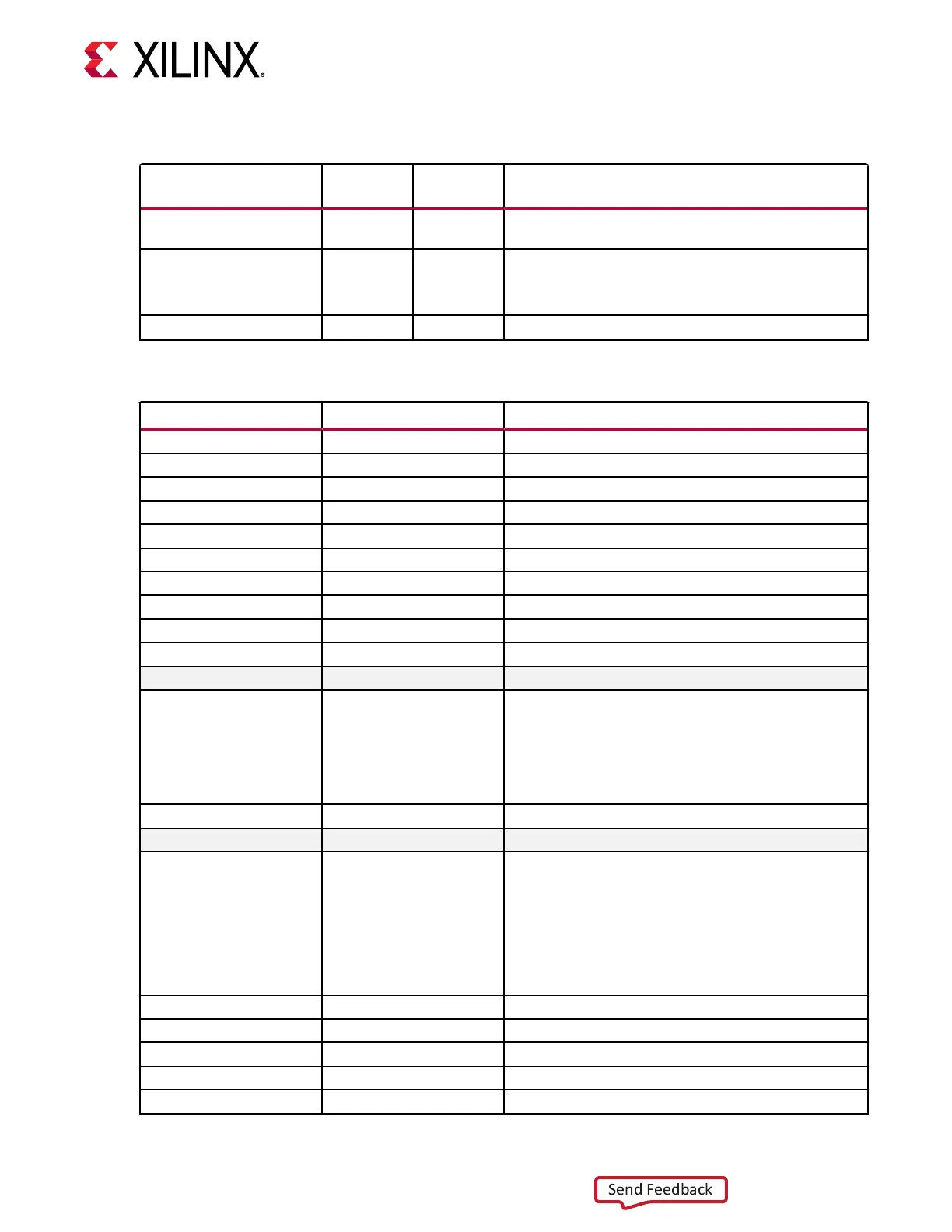

Table 10: LCPLL Attributes

Attributes Type Description

BIAS_CFG0 16-bit Reserved. Use the recommended value from the Wizard.

BIAS_CFG1 16-bit Reserved. Use the recommended value from the Wizard.

BIAS_CFG2 16-bit Reserved. Use the recommended value from the Wizard.

BIAS_CFG3 16-bit Reserved. Use the recommended value from the Wizard.

BIAS_CFG4 16-bit Reserved. Use the recommended value from the Wizard.

A_CFG 16-bit Reserved. Use the recommended value from the Wizard.

CRS_CTRL_CFG0 16-bit Reserved. Use the recommended value from the Wizard.

CRS_CTRL_CFG1 16-bit Reserved. Use the recommended value from the Wizard.

DRPEN_CFG 16-bit Reserved. Use the recommended value from the Wizard.

PLL_CFG0 16-bit Reserved. Use the recommended value from the Wizard.

Bit Name Address Description

LCPLLCLKOUT_RATE [8] Sets the LCPLLCLKOUT_RATE factor either to provide full

LCPLL VCO frequency, or half of LCPLL VCO frequency at the

output:

1'b0: Half rate.

1'b1: Full rate.

PLL_CFG1

16-bit Reserved. Use the recommended value from the Wizard.

Bit Name Address Description

LCPLL_REFCLK_DIV [4:0] LCPLL reference clock divider M settings.

5'b00000: Div by 2.

5'b00001: Div by 3.

5'b00010: Div by 4.

5'b10010: Div by 1.

Other values are not valid.

PLL_CFG2

16-bit Reserved. Use the recommended value from the Wizard.

PLL_CFG3 16-bit Reserved. Use the recommended value from the Wizard.

PLL_CFG4 16-bit Reserved. Use the recommended value from the Wizard.

PLL_CFG5 16-bit Reserved. Use the recommended value from the Wizard.

PLL_CFG6 16-bit Reserved. Use the recommended value from the Wizard.

Chapter 2: Shared Features

UG581 (v1.0) January 4, 2019 www.xilinx.com

Virtex UltraScale+ GTM Transceivers 22

Loading...

Loading...