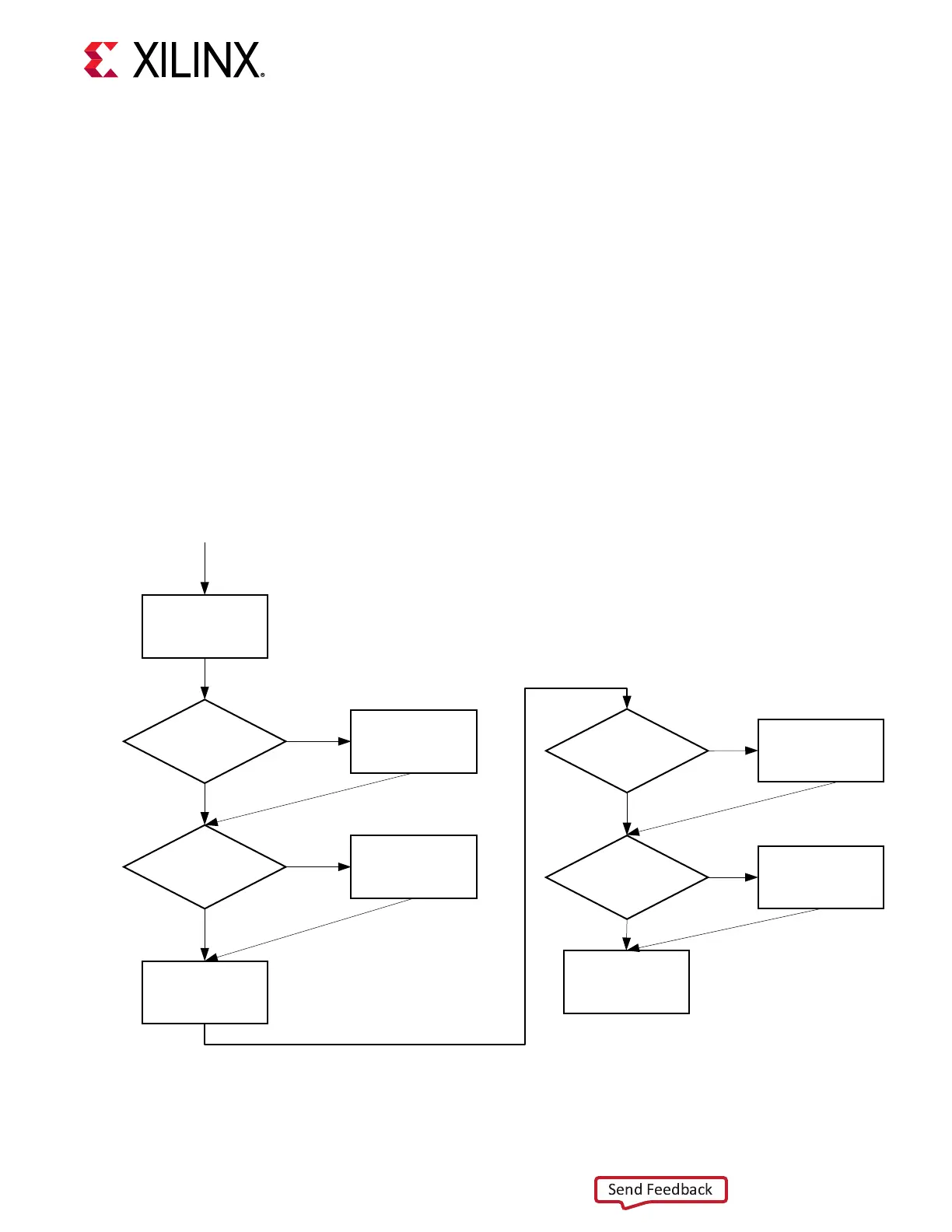

TX Initialization and Reset

The GTM transceiver TX uses a reset state machine to control the reset process. The GTM

transceiver TX is paroned into two reset regions, TX PMA and TX PCS. The paron allows TX

inializaon and reset to be operated only in sequenal mode, as shown in the gure below.

The inializing TX must use GTTXRESET in sequenal mode. Acvang the GTTXRESET input

can automacally trigger a full asynchronous TX reset. The reset state machine executes the

reset sequence, as shown in the gure below, covering the whole TX PMA and TX PCS. During

normal operaon, when needed, sequenal mode allows you to reset the TX from acvang

TXPMARESET and connue the reset state machine unl TXRESETDONE transions from Low

to High.

The TX reset state machine does not reset the PCS unl TXUSERRDY is detected High. Drive

TXUSERRDY High aer all clocks used by the applicaon including TXUSRCLK are shown as

stable.

Figure 13: GTM Transceiver TX Reset State Machine Sequence

Wait until

GTTXRESET from

High to Low

GTTXRESET

High

TX CKCAL Reset

TXPMARESETMASK[0]

= 1?

TXPMARESETMASK[1]

= 1?

TX PMA Top Reset

Yes

No

TXPCSRESETMASK[0]

= 1?

TX FEC Reset

Yes

No

TXPCSRESETMASK[1]

= 1?

TX PCS Top Reset

TXRESETDONE High

Yes

Yes

No

No

Wait for TXUSERRDY

= 1

X20905-060518

Chapter 2: Shared Features

UG581 (v1.0) January 4, 2019 www.xilinx.com

Virtex UltraScale+ GTM Transceivers 27

Loading...

Loading...