GTM Transceiver TX Reset in Response to Completion

of Configuration

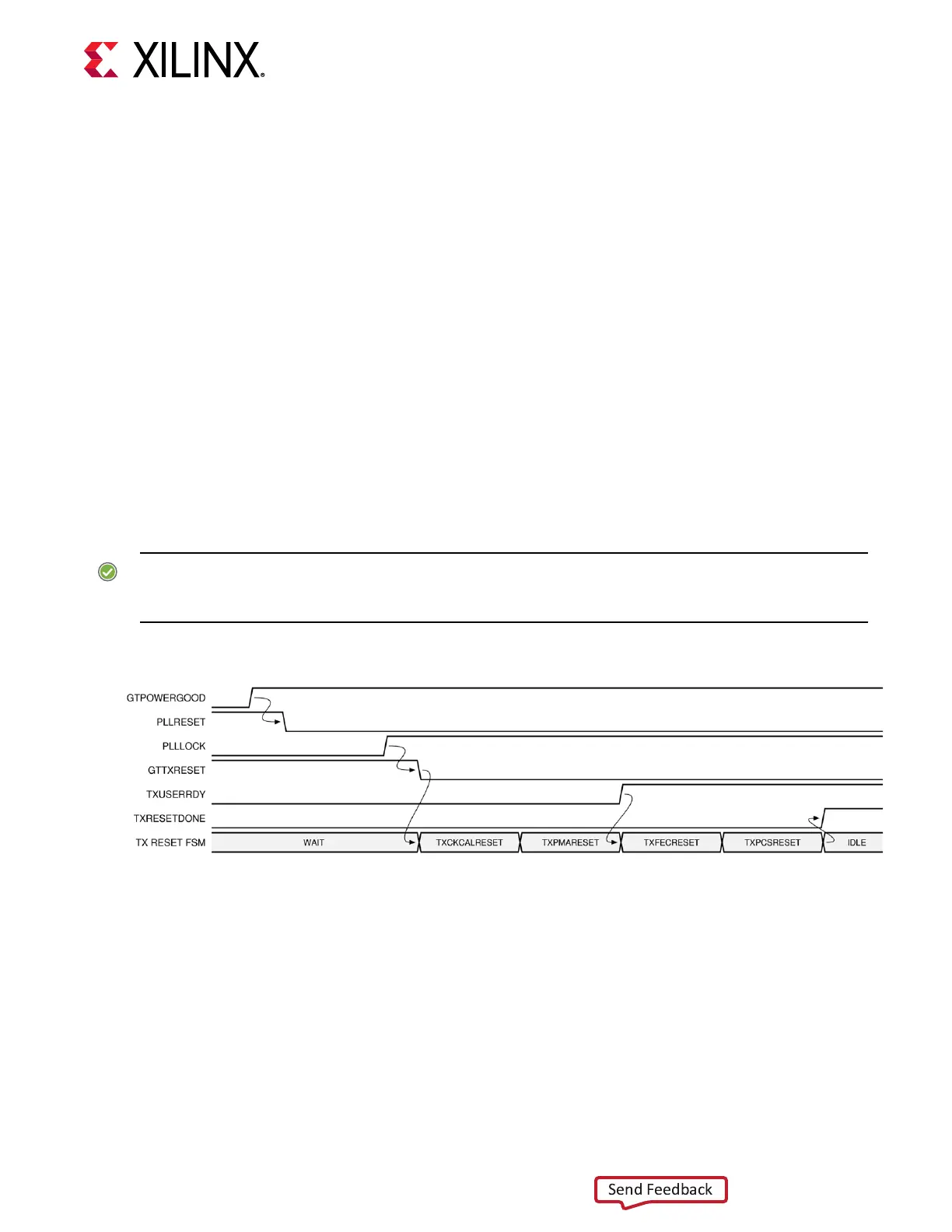

The TX reset sequence shown in TX Inializaon and Reset is not automacally started to follow

global GSR. It must meet these condions:

1. TXRESETMODE must be set to sequenal mode.

2. GTTXRESET must be used.

3. All TXPMARESETMASK and TXPCSRESETMASK bits should be set to High.

4. GTTXRESET cannot be driven Low unl the associated PLL is locked.

5. Ensure that GTPOWERGOOD is High before releasing PLLRESET and GTTXRESET.

If the reset mode is defaulted to single mode, then you must:

1. Wait another 300–500 ns.

2. Assert PLLRESET and GTTXRESET following the reset sequence described in the following

gure.

RECOMMENDED: Use the associated PLLLOCK from the PLL to release GTTXRESET from High to

Low as shown in the gure. The TX reset state machine waits when GTTXRESET is detected High and

starts the reset sequence unl GTTXRESET is released Low.

Figure 14: GTM Transmitter Initialization after Configuration

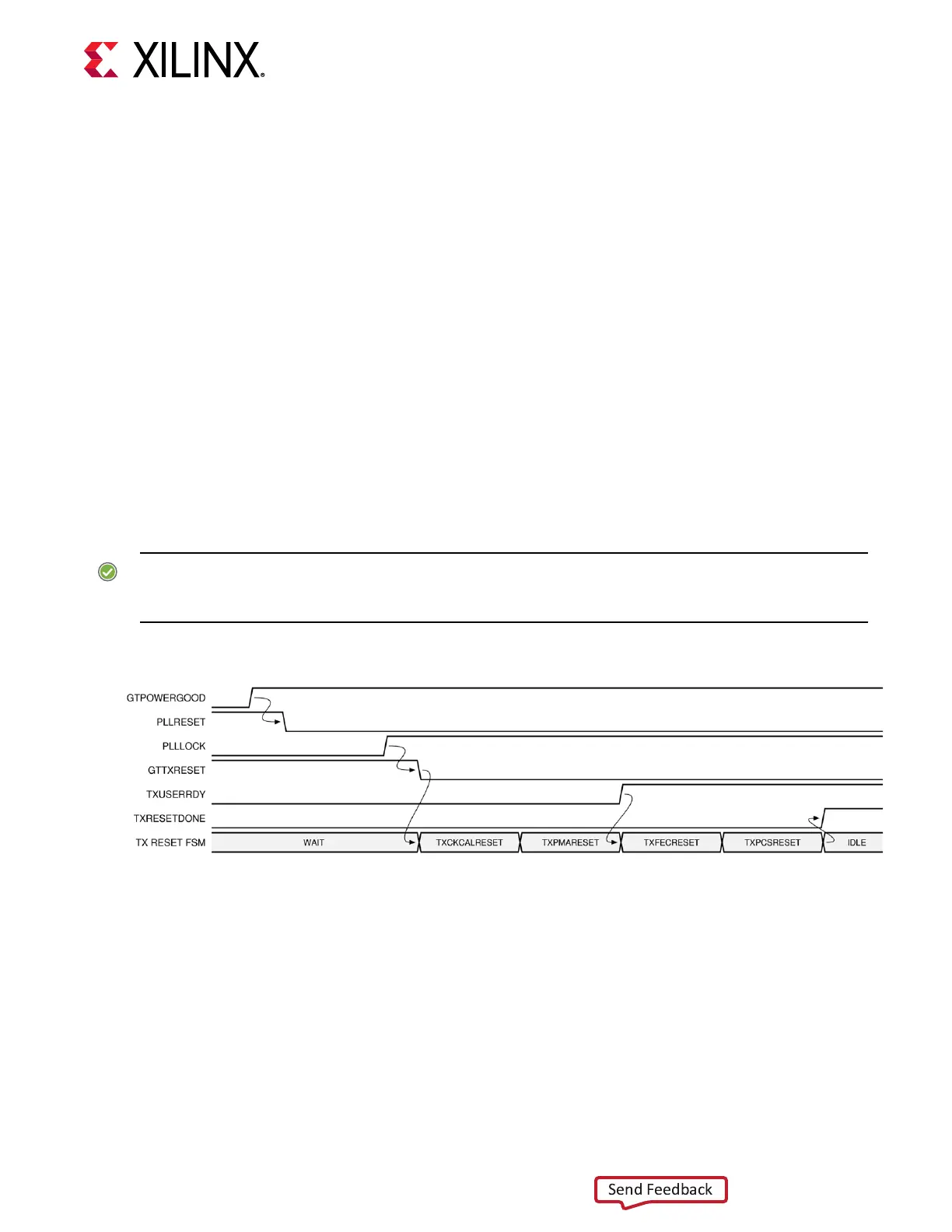

GTM Transceiver TX Reset in Response to GTTXRESET

Pulse in Full Sequential Reset

The GTM transceiver allows you to reset the enre TX completely at any me by sending

GTTXRESET an acve-High pulse. These condions must be met when using GTTXRESET:

1. TXRESETMODE must be set to sequenal mode.

2. All TXPMARESETMASK and TXPCSRESETMASK bits should be held High during the reset

sequence before TXRESETDONE is detected High.

Chapter 2: Shared Features

UG581 (v1.0) January 4, 2019 www.xilinx.com

Virtex UltraScale+ GTM Transceivers 30

Loading...

Loading...