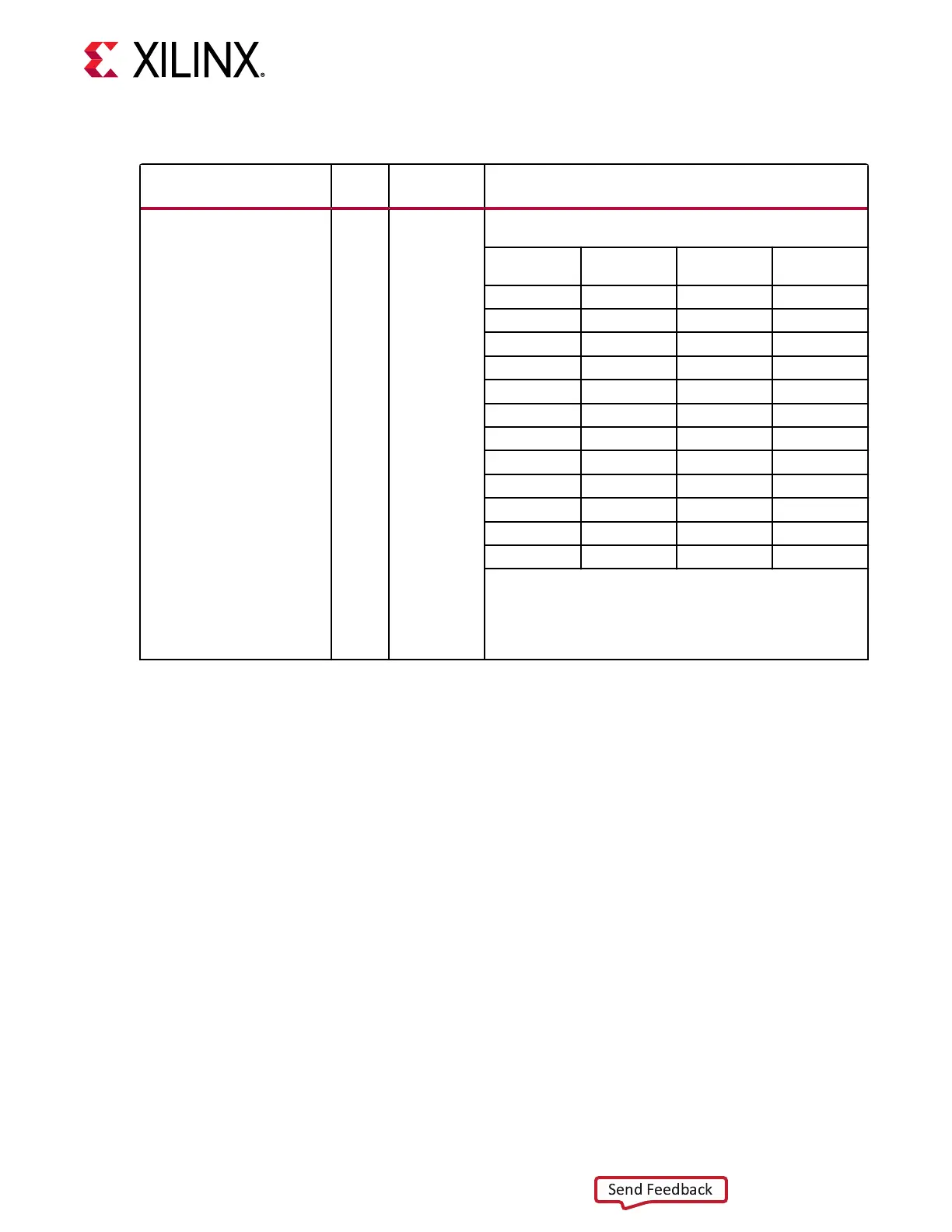

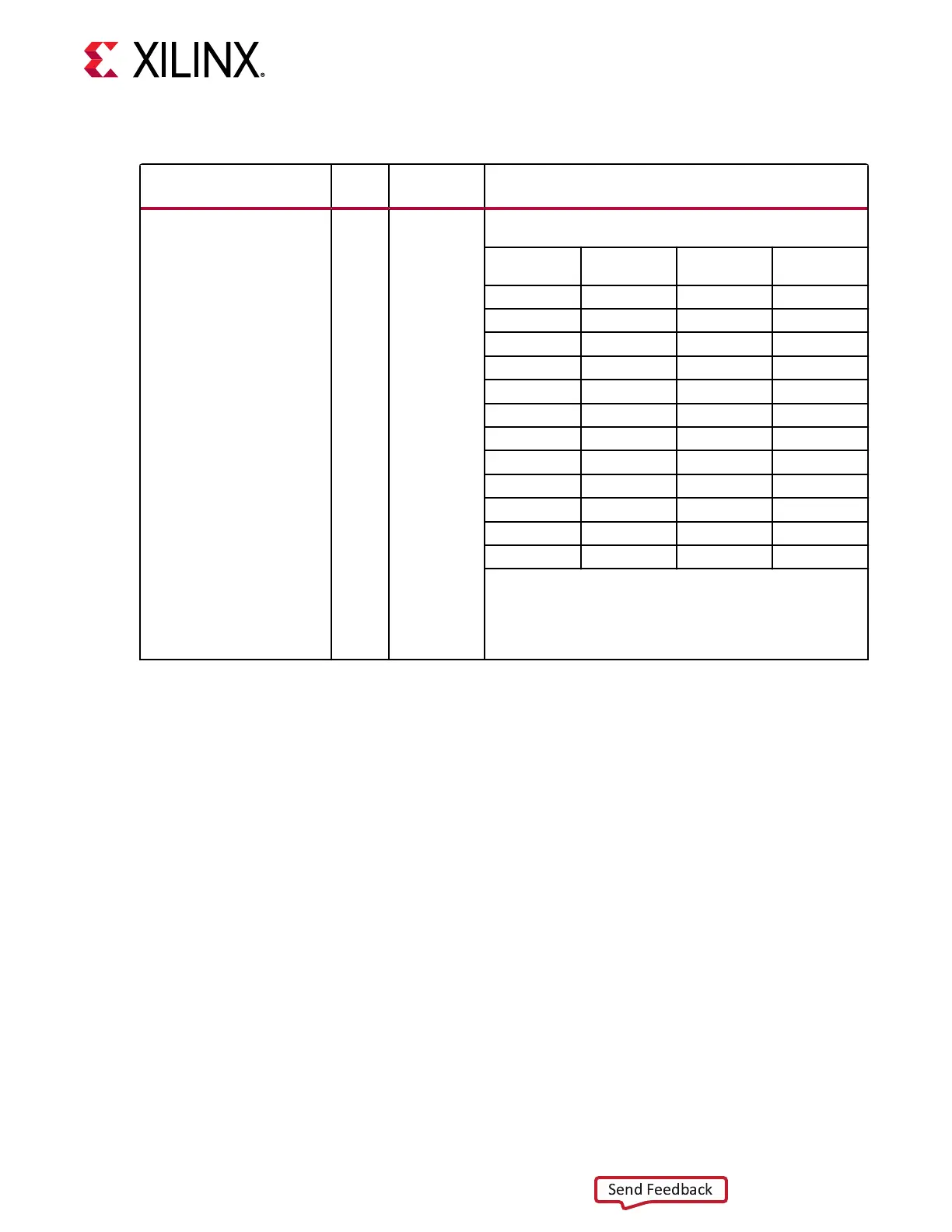

Table 46: TX Configurable Driver Ports (cont'd)

Port Dir

Clock

Domain

Description

CH[0/1]_TXEMPPRE2[3:0] Input Async Transmitter pre-cursor 2 TX pre-emphasis control for channel 0.

The default is user specified. All listed values (dB) are typical

[4:0] dB (PAM4) dB (NRZ) Coefficient

Units

4’b0000

0.0 0.0 0

4’b0001

–0.3 –0.2 1

4’b0010

–0.7 –0.5 2

4’b0011

–1.1 –0.7 3

4’b0100

–1.5 –0.9 4

4’b0101

–1.9 –1.2 5

4’b0110

–2.3 –1.5 6

4’b0111

–2.7 –1.7 7

4’b1000

N/A –2.0 8

4’b1001

N/A –2.3 9

4’b1010

N/A –2.6 10

4’b1011

N/A –2.9 11

Notes:

1. The peak-to-peak differential voltage is defined when

CH[0/1]_TXEMPPRE = 5’b00000, and CH[0/1]_TXEMPPOST

= 4’b0000. Emphasis = 20log10(V

high

/V

low

) = |

20log10(V

low

/V

high

)|.

Chapter 3: Transmitter

UG581 (v1.0) January 4, 2019 www.xilinx.com

Virtex UltraScale+ GTM Transceivers 81

Loading...

Loading...