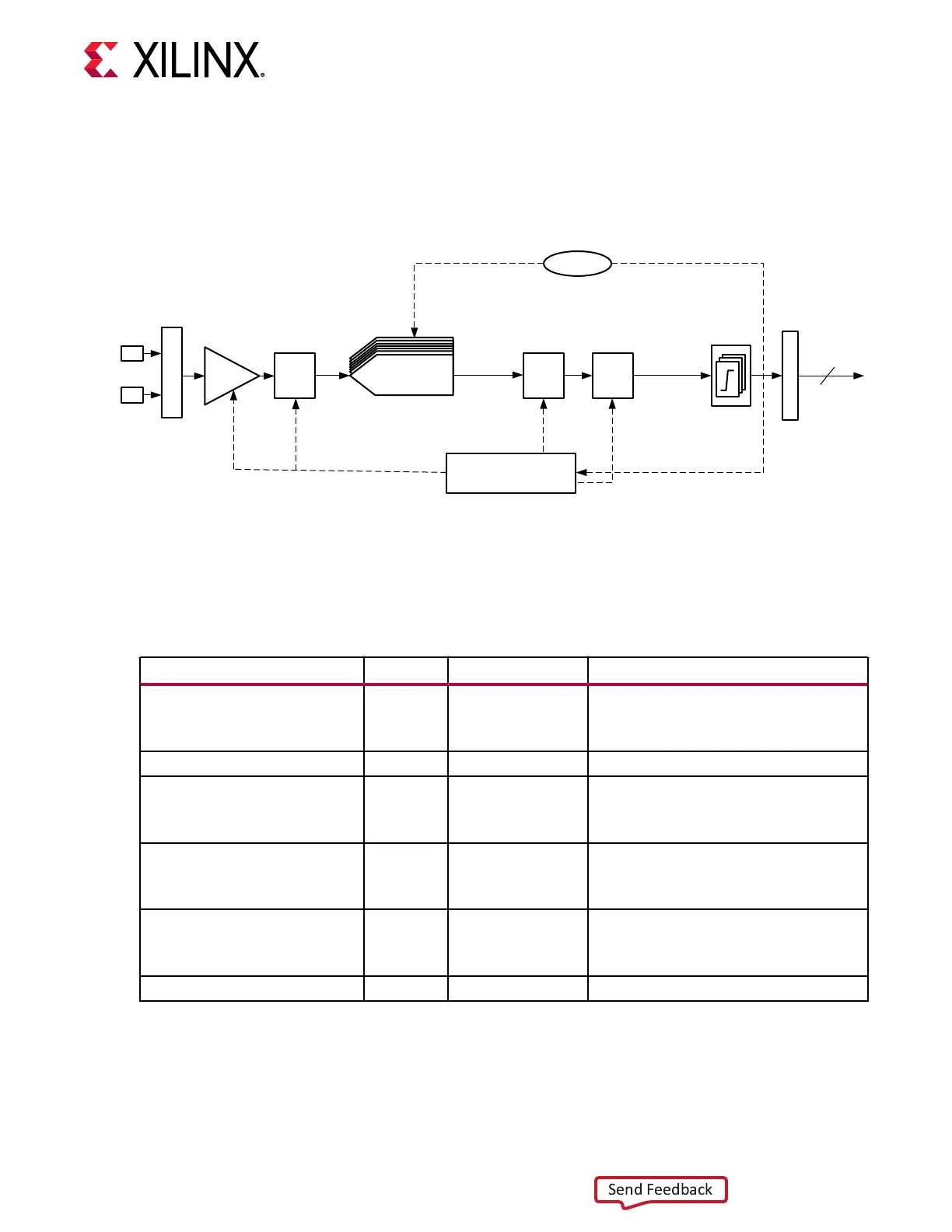

The combinaon of CTLE, FFE, and DFE can compensate for both the pre-cursor and post-cursor

of the transmied bit. All equalizaon loops are auto-adapve to handle a wide range of channel

proles and to compensate for any PVT variaons.

Figure 39: GTM RX Equalization

Adaptation

Controller

CDR

Termination

P

N

AGC

ADC

FFE DFE

SIPO

CTLE

Data to PCS

X20924-053118

Ports and Attributes

The following table denes the RX equalizer ports.

Table 50: RX Equalizer Ports

Port Dir Clock Domain Description

CH[0/1]_RXADAPTRESET In Async This port is driven High and then deasserted

to start a single-mode reset on RX adaptation.

The reset is not dependent on RXRESETMODE

or RXPMARESETMASK setting.

CH[0/1]_RXADCCALRESET In Async Reserved. Tie to 1’b0.

CH[0/1]_RXADCCLKGENRESET In Async This port is driven High and then deasserted

to start a single-mode reset on the RX ADC

CLKGEN. The reset is not dependent on

RXRESETMODE or RXPMARESETMASK setting.

CH[0/1]_RXDFERESET In Async This port is driven High and then deasserted

to start a single-mode reset on the DFE. The

reset is not dependent on RXRESETMODE or

RXPMARESETMASK setting.

CH[0/1]_RXDSPRESET In Async This port is driven High and then deasserted

to start a single-mode reset on the DSP. The

reset is not dependent on RXRESETMODE or

RXPMARESETMASK setting.

CH[0/1]_RXEQTRAINING In Async Reserved. Tie to 1'b0.

The following table denes the RX equalizer aributes.

Chapter 4: Receiver

UG581 (v1.0) January 4, 2019 www.xilinx.com

Virtex UltraScale+ GTM Transceivers 88

Loading...

Loading...