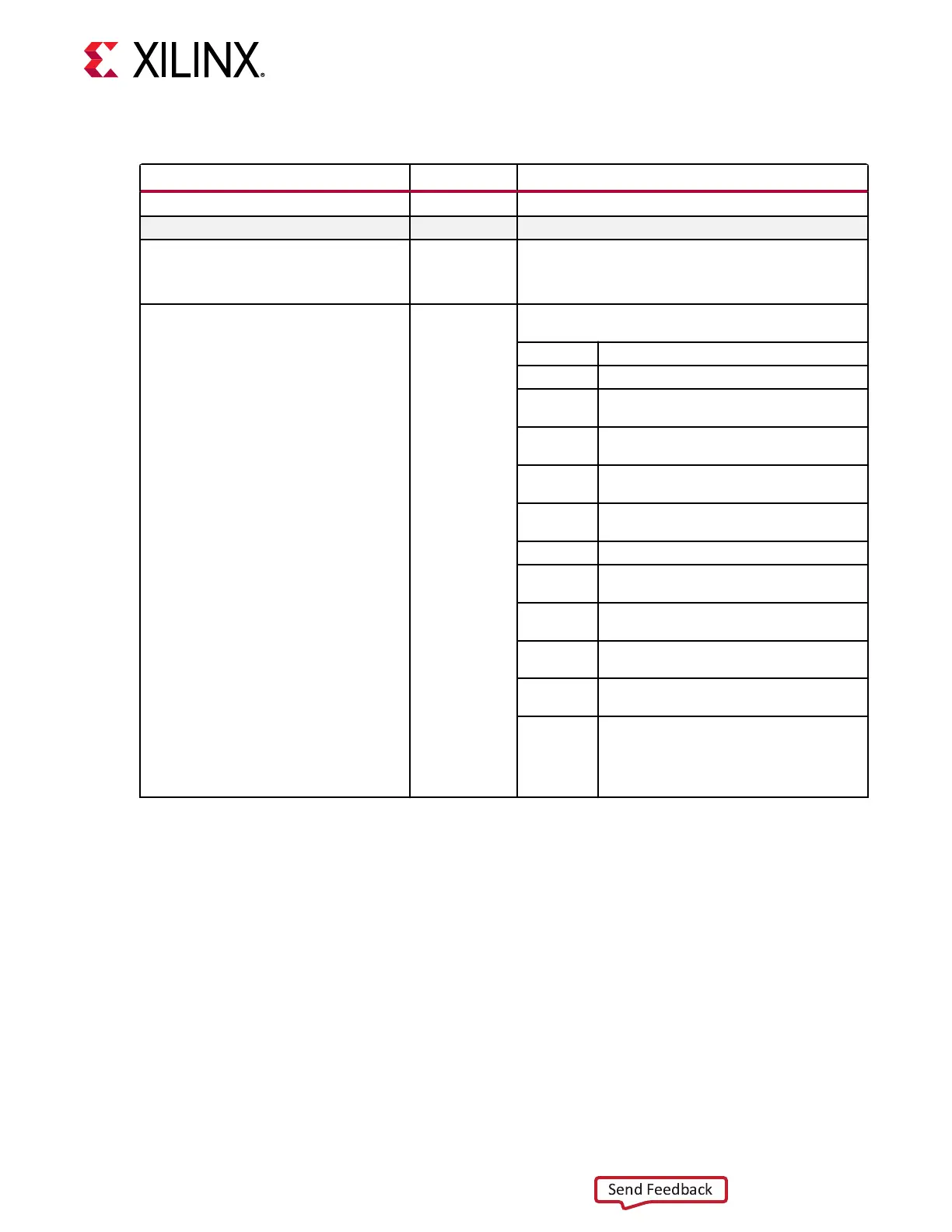

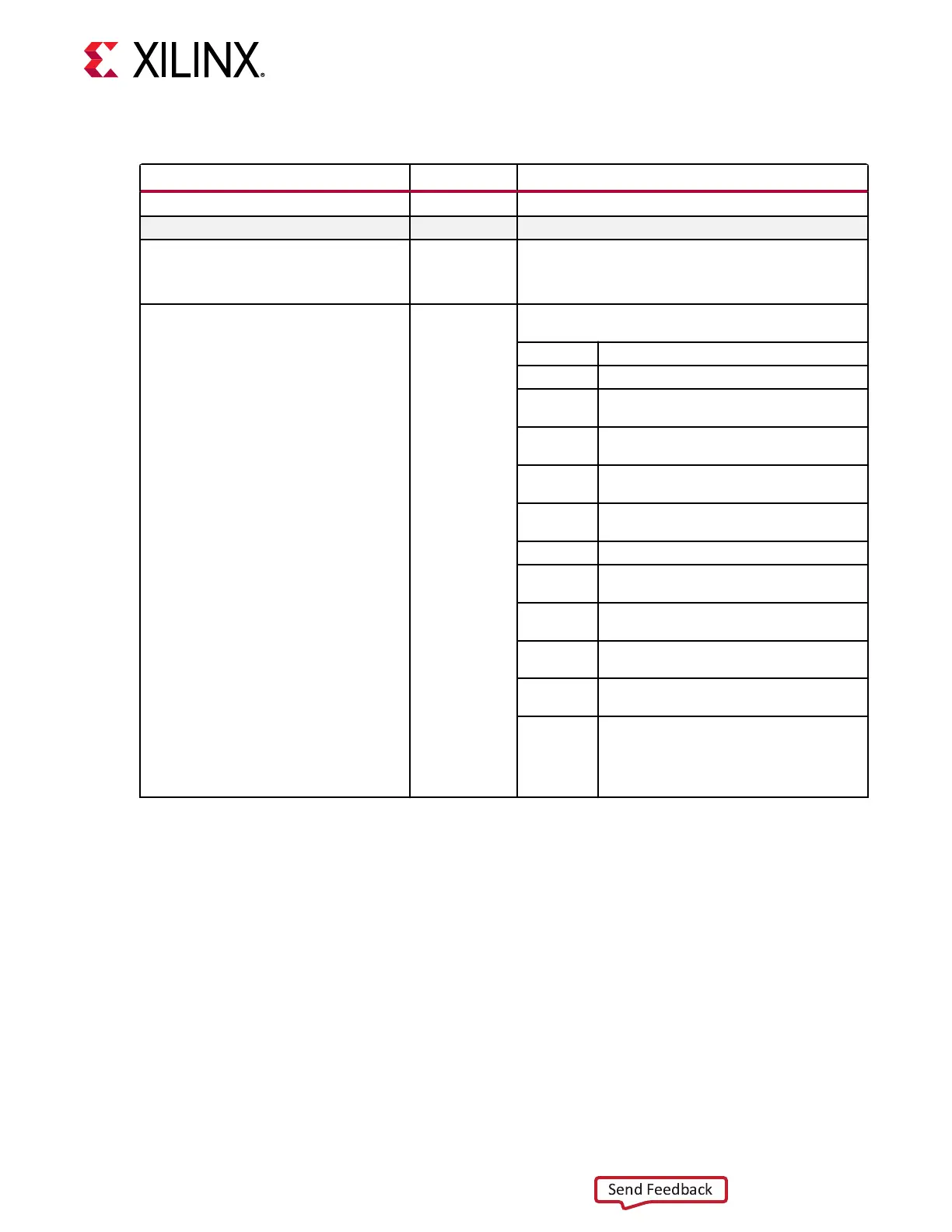

Table 51: RX Equalizer Attributes

Attribute Type Description

CH[0/1]_RX_APT_CTRL_CFG2 16-bit Reserved.

Bit Name Address Description

RXMODSEL [3] Receiver input modulation control.

0’b0: PAM4 modulation.

0’b1: NRZ modulation.

CH[0/1]_RX_APT_CFG27A[15:0] 16-bit Adaptation loop freeze controls. Use the recommended

value from the Wizard.

Bit Description

[15:13] Reserved.

[12] Enable to freeze current automatic gain

control (AGC) adapt value.

[11] Enable to freeze current CTLE High

frequency loop (KH) adapt value.

[10] Enable to freeze current CTLE Low

frequency loop (KL) adapt value.

[9] Enable to freeze current Offset Cancelation

(OS) adapt value.

[8:5] Reserved.

[4] Enable to freeze current FFE Tap HM4 adapt

value.

[3] Enable to freeze current FFE Tap HM3 adapt

value.

[2] Enable to freeze current FFE Tap HM2 adapt

value.

[1] Enable to freeze current FFE Tap HM1 adapt

value.

[0] Adaptation freeze control. This bit must be

enabled to freeze the loops selected in

CH[0/1]_RX_APT_CFG27A, and

CH[0/1]_RX_APT_CFG27B. If this bit is set to

Low, all loops will be auto-adapting.

Chapter 4: Receiver

UG581 (v1.0) January 4, 2019 www.xilinx.com

Virtex UltraScale+ GTM Transceivers 89

Loading...

Loading...