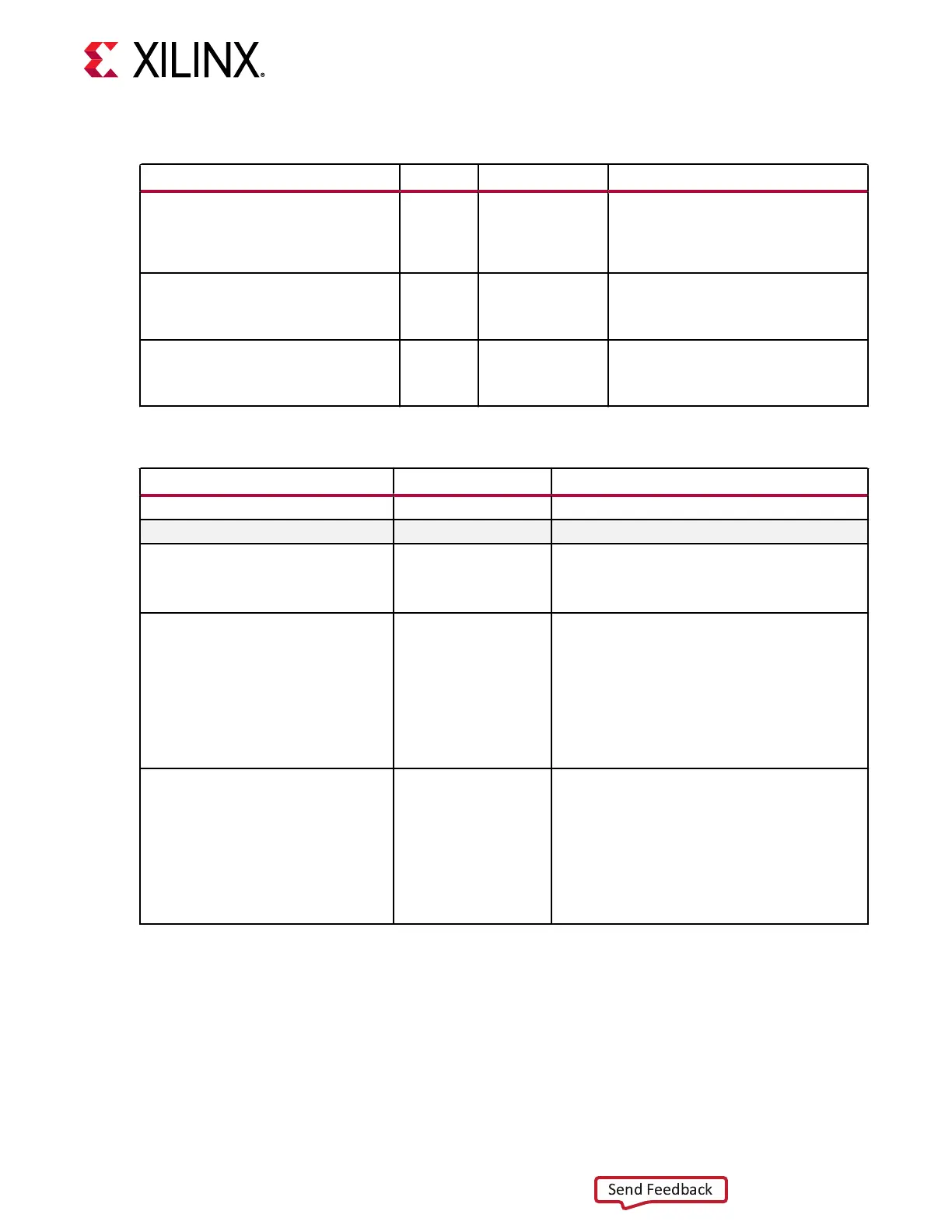

Table 54: RX Programmable Divider Ports

Port Dir Clock Domain Description

CH[0/1]_RXPROGDIVRESET In Async This active-High port resets the dividers as

well as the RXPRGDIVRESETDONE

indicator. A reset must be performed

whenever the input clock source is

interrupted.

CH[0/1]_RXPRGDIVRESETDONE

Out Async When the input clock is stable and reset is

performed, this active-High signal

indicates the reset is completed and the

output clock is stable.

CH[0/1]_RXPROGDIVCLK Out Clock RXPROGDIVCLK is the parallel clock output

from The RX programmable divider. This

clock is the recommended output to the

interconnect logic through BUFG_GT.

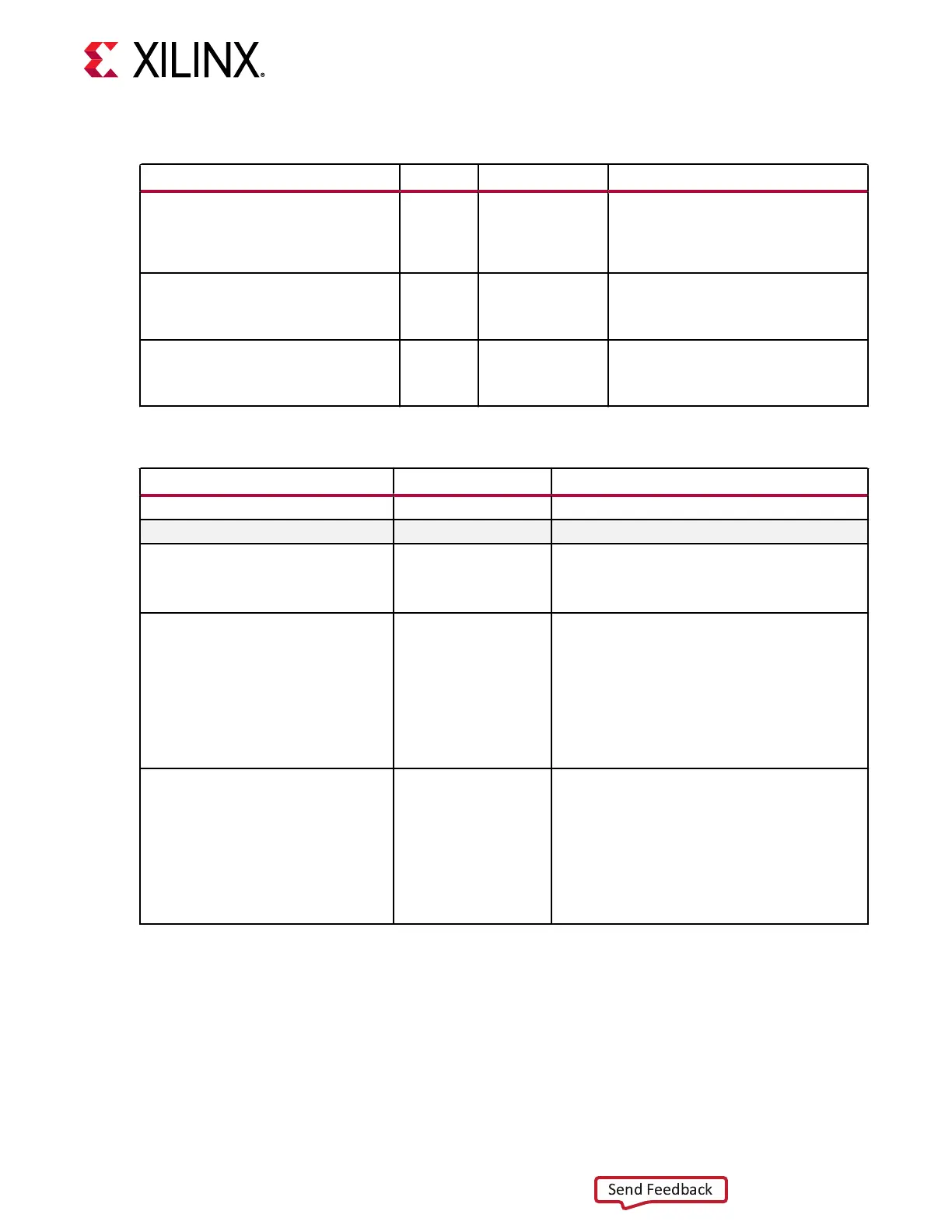

Table 55: RX Programmable Divider Attribute

Attribute Type Description

CH[0/1]_RX_ANA_CFG1 16-bit Reserved.

Bit Name Address Description

RX_PROGDIV_SELFR [13] This attribute is used during the RX programmable

divider ratio selection. Set to 1’b1 to obtain the full

rate of the divided clock. Set to 1’b0 to obtain the

half rate of the divided clock.

RX_PROGDIV_SEL_DIV66 [12] This attribute is used during the RX programmable

divider ratio selection.

• The attribute must be set to 1’b1 when the

desired divider value is either 16.5, 33, 66, or

132.

• For all other divider values, this should be set to

1’b0.

RX_PROGDIV_SEL_DIV5

[11] This attribute is used during the RX programmable

divider ratio selection.

• The attribute must be set to 1’b0 when the

desired divider value is either 16.5, 33, 66, or

132.

• For all other divider values, this should be set to

1’b1.

Chapter 4: Receiver

UG581 (v1.0) January 4, 2019 www.xilinx.com

Virtex UltraScale+ GTM Transceivers 96

Loading...

Loading...