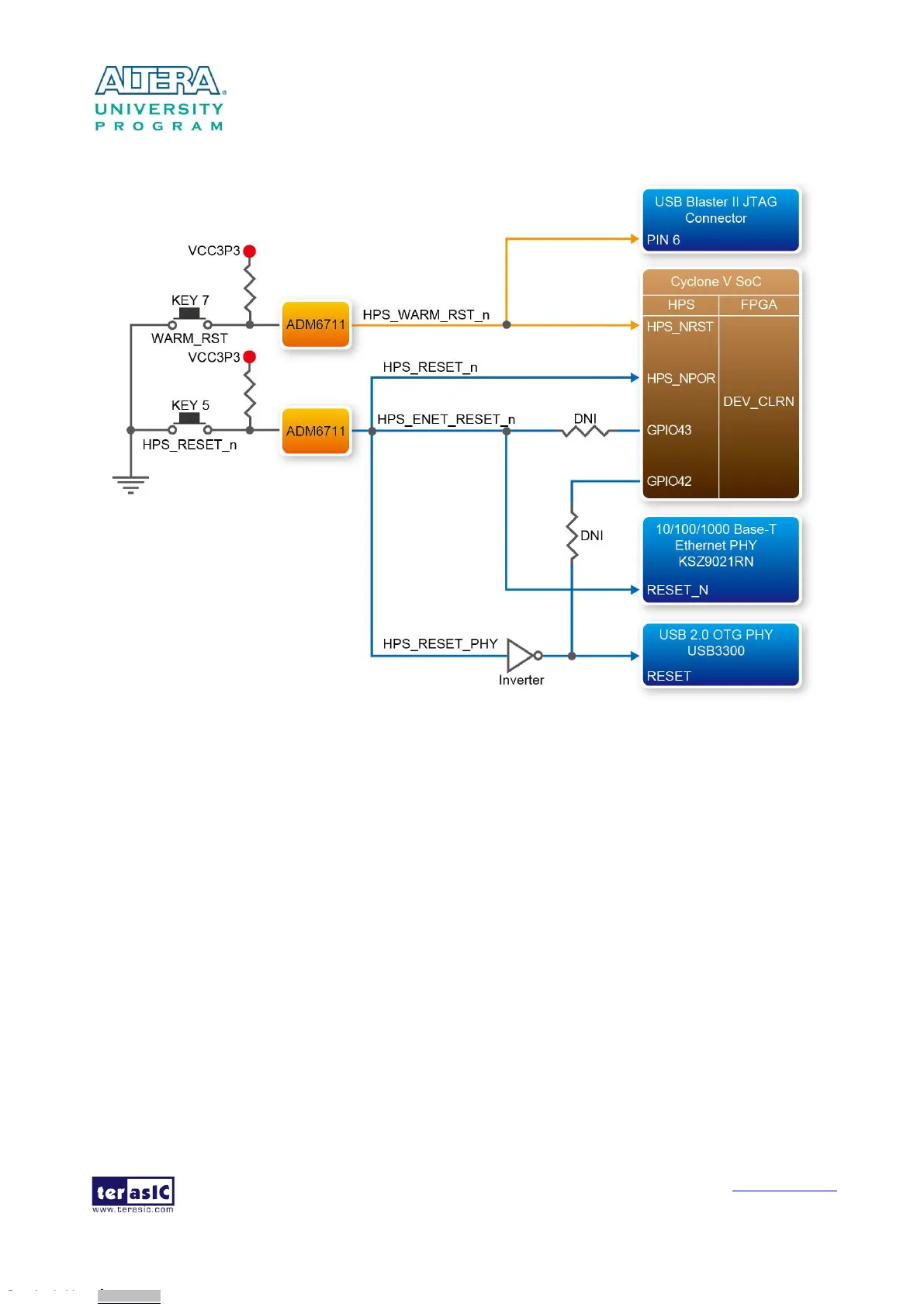

Figure 3-11 HPS reset tree on DE1-SoC board

3

3

.

.

5

5

C

C

l

l

o

o

c

c

k

k

C

C

i

i

r

r

c

c

u

u

i

i

t

t

r

r

y

y

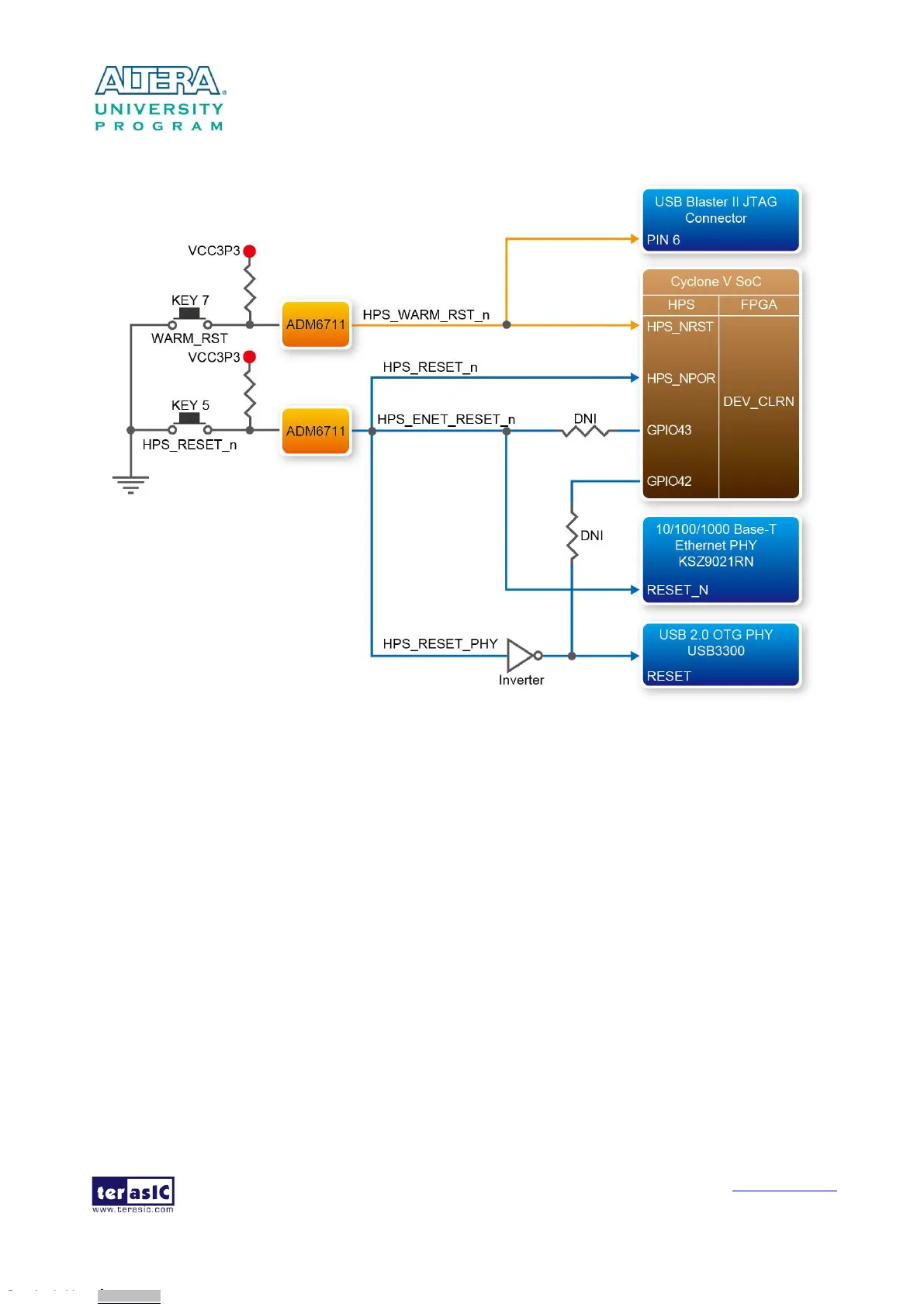

Figure 3-12 shows the default frequency of all external clocks to the Cyclone V SoC FPGA. A

clock generator is used to distribute clock signals with low jitter. The four 50MHz clock signals

connected to the FPGA are used as clock sources for user logic. One 25MHz clock signal is

connected to two HPS clock inputs, and the other one is connected to the clock input of Gigabit

Ethernet Transceiver. Two 24MHz clock signals are connected to the clock inputs of USB

Host/OTG PHY and USB hub controller. The associated pin assignment for clock inputs to FPGA

I/O pins is listed in Table 3-5.

Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.

Loading...

Loading...