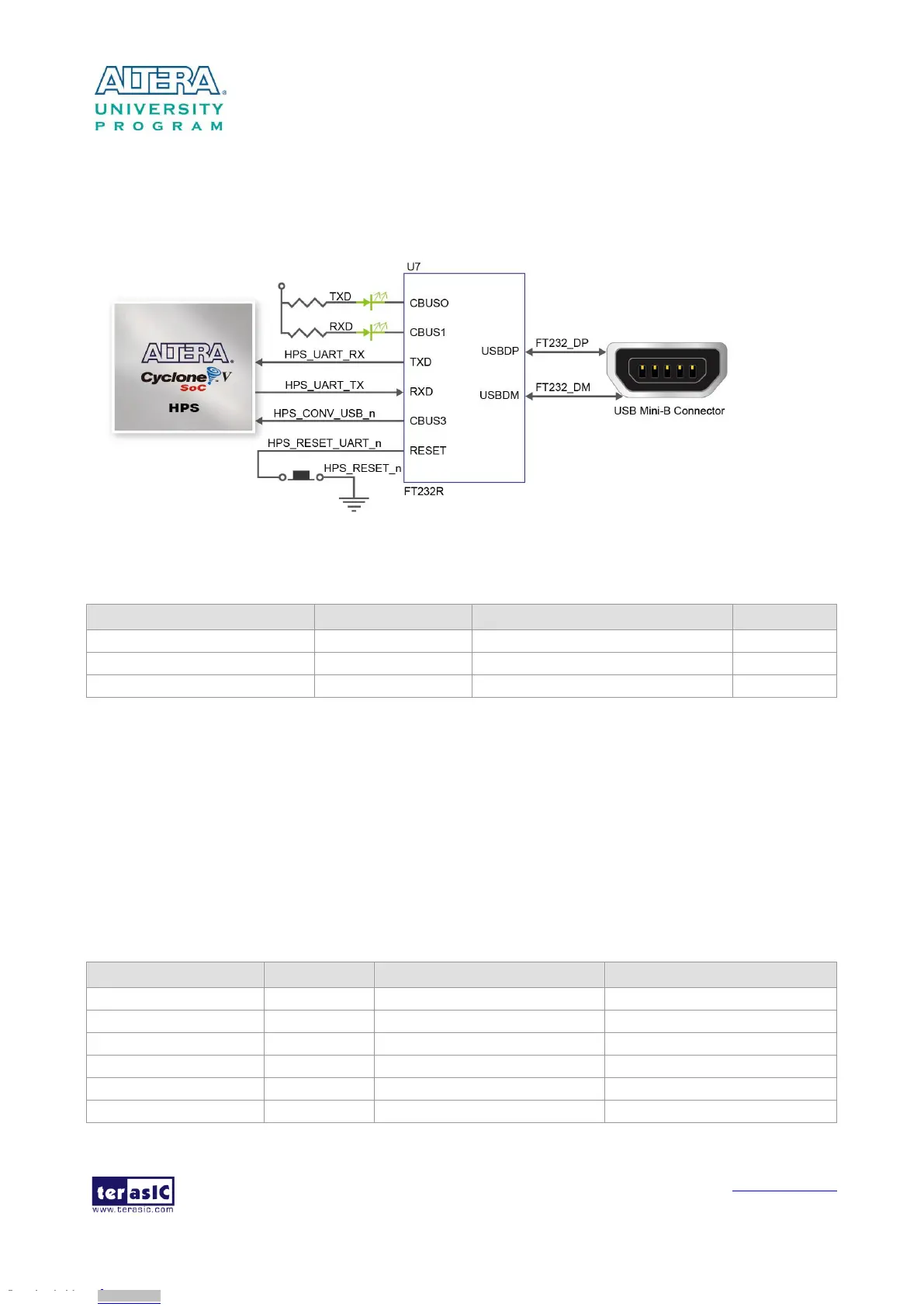

USB of DE1-SoC system CD. Figure 3-32 shows the connections between the HPS, FT232R chip,

and the USB Mini-B connector. Table 3-26 lists the pin assignment of UART interface connected to

the HPS.

Figure 3-32 Connections between the HPS and FT232R Chip

Table 3-26 Pin Assignment of UART Interface

3

3

.

.

7

7

.

.

4

4

D

D

D

D

R

R

3

3

M

M

e

e

m

m

o

o

r

r

y

y

The DDR3 devices connected to the HPS are the exact same model as the ones connected to the

FPGA. The capacity is 1GB and the data bandwidth is in 32-bit, comprised of two x16 devices with

a single address/command bus. The signals are connected to the dedicated Hard Memory Controller

for HPS I/O banks and the target speed is 400 MHz. Table 3-27 lists the pin assignment of DDR3

and its description with I/O standard.

Table 3-27 Pin Assignment of DDR3 Memory

Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.

Loading...

Loading...