Description of fields within Sub-Register 0x24:00 EC_CTRL

External timebase reset mode enable. See section 6.1.1 – One Shot Timebase Reset (OSTR)

Mode.

7.2.37.2 Sub-Register 0x24:04 EC_RXTC

External clock synchronisation counter captured on

RMARKER.

Register file: 0x24 – External Synchronisation Control, sub-register 0x04 is the External clock synchronisation

counter value captured on RMARKER, EC_RXTC. The EC_RXTC register is used to timestamp the received

packet with respect to the external clock, see section 6.1.3 – One Shot Receive Synchronisation (OSRS) Mode

for details of the procedure. The EC_RXTC register contains the following sub-fields:

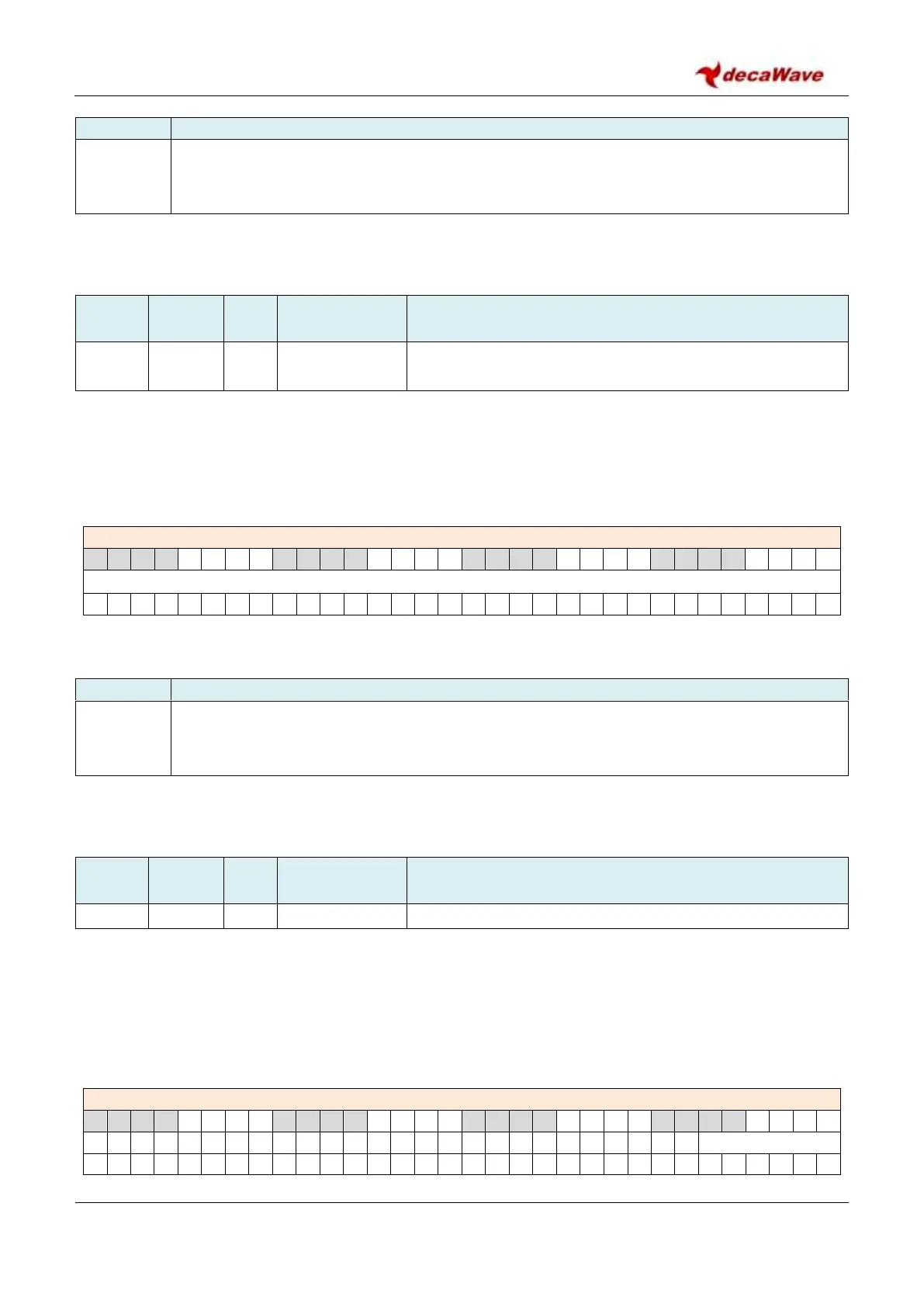

REG:24:04 – EC_RXTC– External clock synchronisation timestamp capture

The fields of the EC_RXTC register identified above are individually described below:

Description of fields within Sub-Register 0x24:04 EC_RXTC

RX_TS_EST

reg:24:04

bits:31:0

External clock synchronisation counter captured on RMARKER. See section 6.1.3 – One Shot

Receive Synchronisation (OSRS) Mode.

7.2.37.3 Sub-Register 0x24:08 EC_GOLP

External clock offset to first path 1 GHz counter

Register file: 0x24 – External Synchronisation Control, sub-register 0x08 is the External clock offset to first

path 1 GHz counter, EC_GOLP. The EC_GOLP register is used to time the offset in 1 GHz intervals between

the RMARKER, and the next edge of the external clock. This value can be used to calculate range with

respect to the external clock, see section 6.1.3 – One Shot Receive Synchronisation (OSRS) Mode for details

of the procedure. The EC_GOLP register contains the following sub-fields:

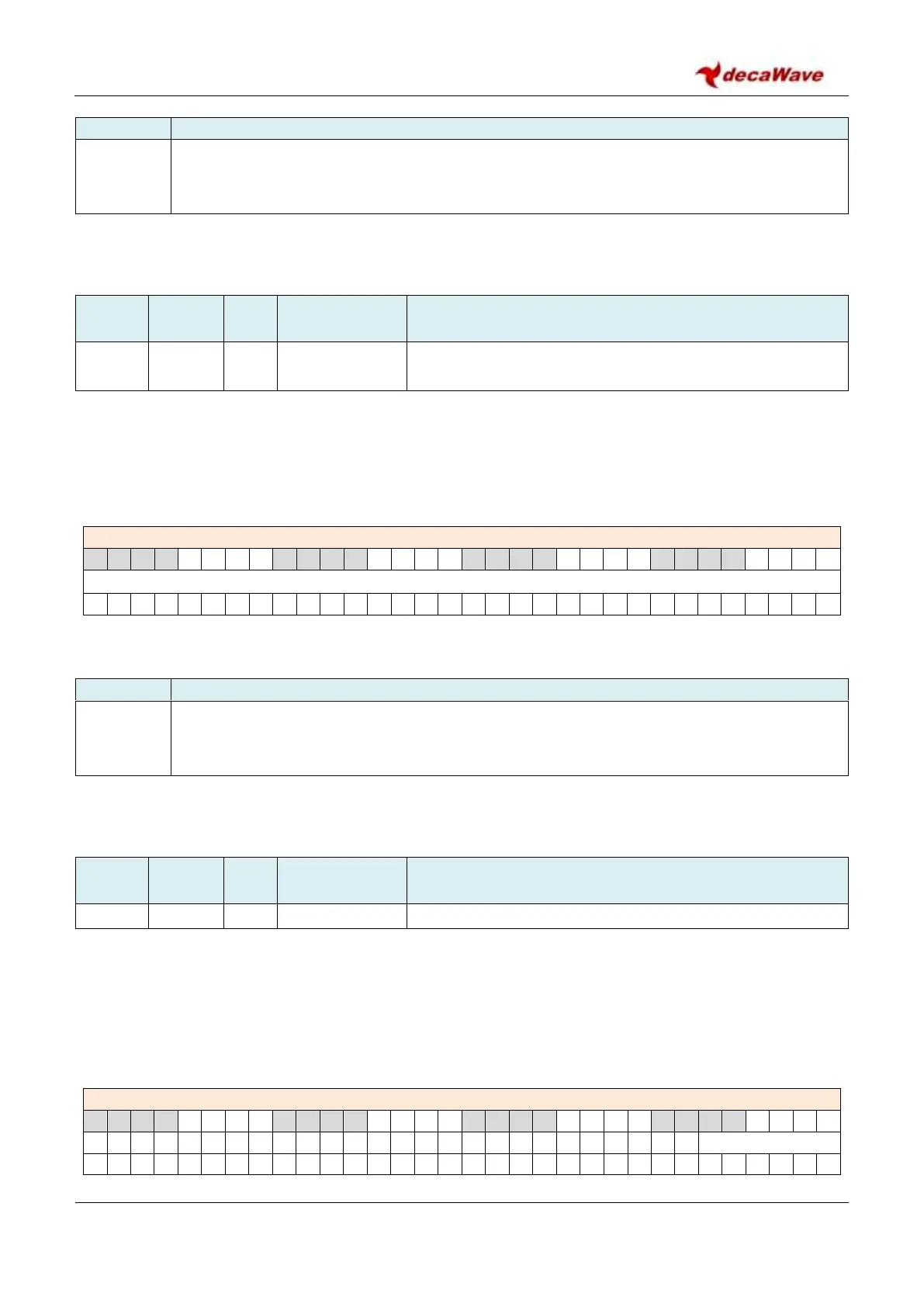

REG:24:08– EC_GOLP– External clock offset to first path 1 GHz counter

Loading...

Loading...