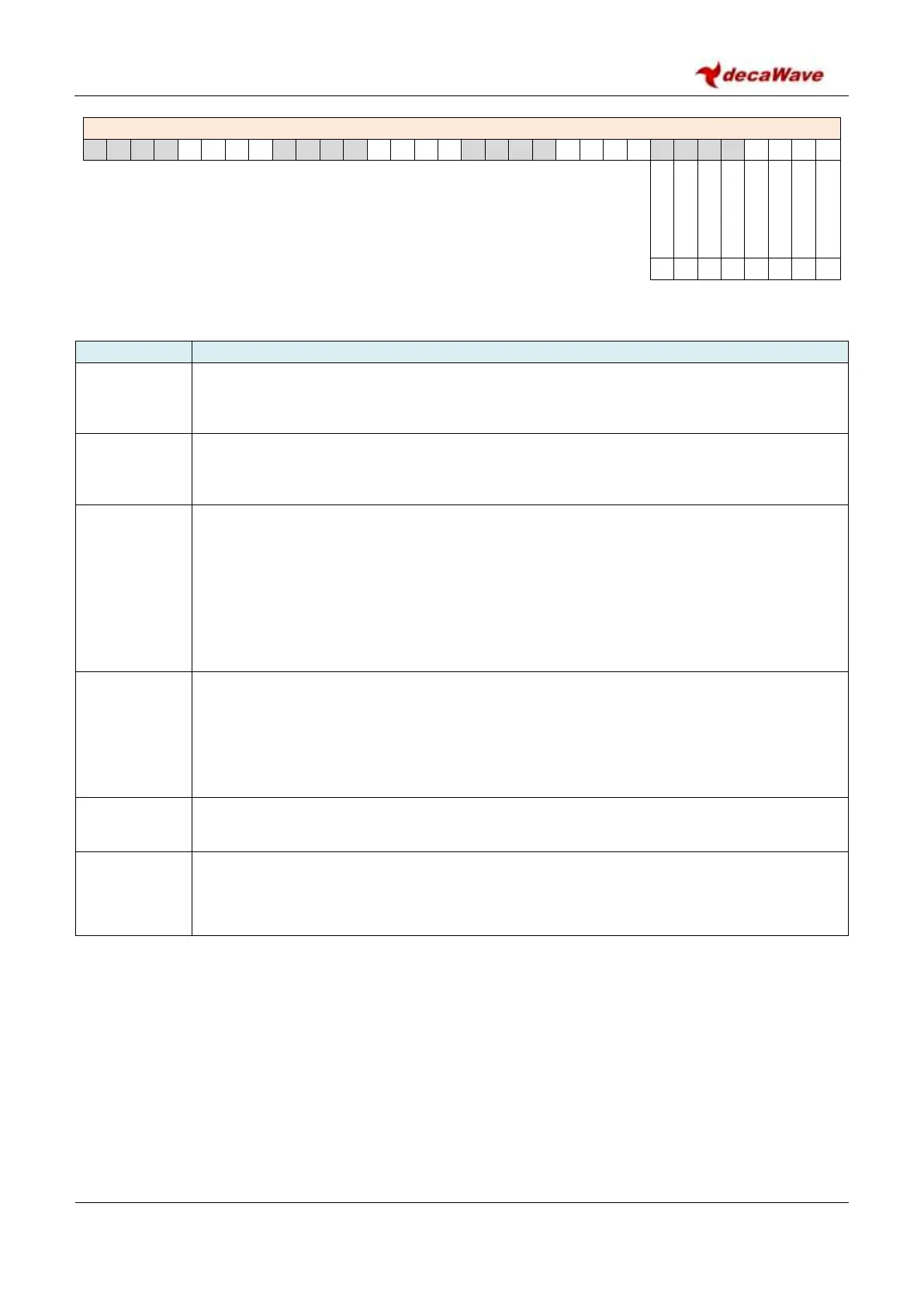

REG:2C:02 – AON_CTRL – AON Control Register

Definition of the bit fields within Sub-Register 0x2C:02 – AON_CTRL:

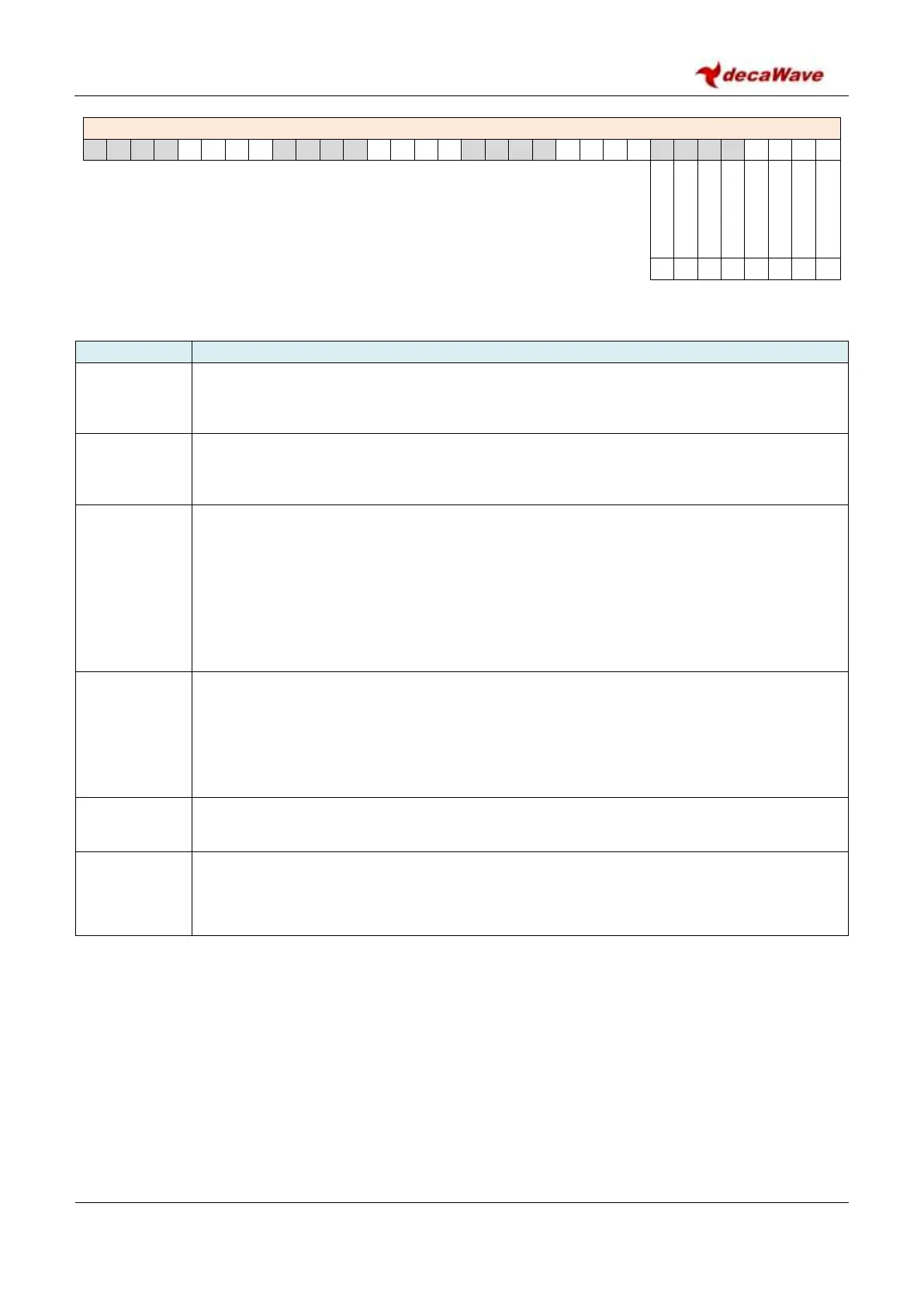

Description of fields within Sub-Register 0x2C:02 – AON_CTRL

When this bit is set the DW1000 will copy the user configurations from the AON memory to

the host interface register set. The RESTORE bit will auto clear when this command is

executed.

When this bit is set the DW1000 will copy the user configurations from the host interface

register set into the AON memory. It will then proceed to upload the AON block

configurations. The SAVE bit will auto clear when this command is executed.

Upload the AON block configurations to the AON. This control will copy the AON

configurations of the two registers: Sub-Register 0x2C:06 – AON_CFG0 and Sub-Register

0x2C:0A – AON_CFG1 into the AON configuration registers. This may be done for instance

to enter SLEEP mode after correctly configuring it in those two registers, although SLEEP

may be automatically entered under certain conditions by appropriate configurations within

Register file: 0x36 – Power Management and System Control. If the UPL_CFG is being set

for a purpose other than going to sleep then needs to be explicitly cleared immediately

after use as it is not self-clearing.

Direct AON memory access read. When this bit is set, (and direct access is enabled via the

DCA_ENAB bit below), it commands a direct read of the low-power configuration array

store memory. The address to read from is specified in Sub-Register 0x2C:04 – AON_ADDR

and the resultant read data is presented in Sub-Register 0x2C:03 – AON_RDAT. This access

is needed to retrieve the result of a calibration measurement on the low-power oscillator,

see LPOSC_CAL bit in Sub-Register 0x2C:0A – AON_CFG1.

Bits marked ‘-’ in register 0x2C:02 are reserved and should always be written as zero to

avoid any malfunction of the DW1000.

Direct AON memory access enable bit. This bit needs to be set to 1 to enable the

DCA_READ above to operate. Note: DCA_ENAB must to be reset to 0 to allow the automatic

saving/restoring of user configurations to/from the AON memory, as needed for correct

operation during entry and exit from SLEEP and DEEPSLEEP modes.

Loading...

Loading...