Table 50: Sub-Register 0x2E:1806– LDE_CFG2 values

Value to program to

Sub-Register 0x2E:1806– LDE_CFG2

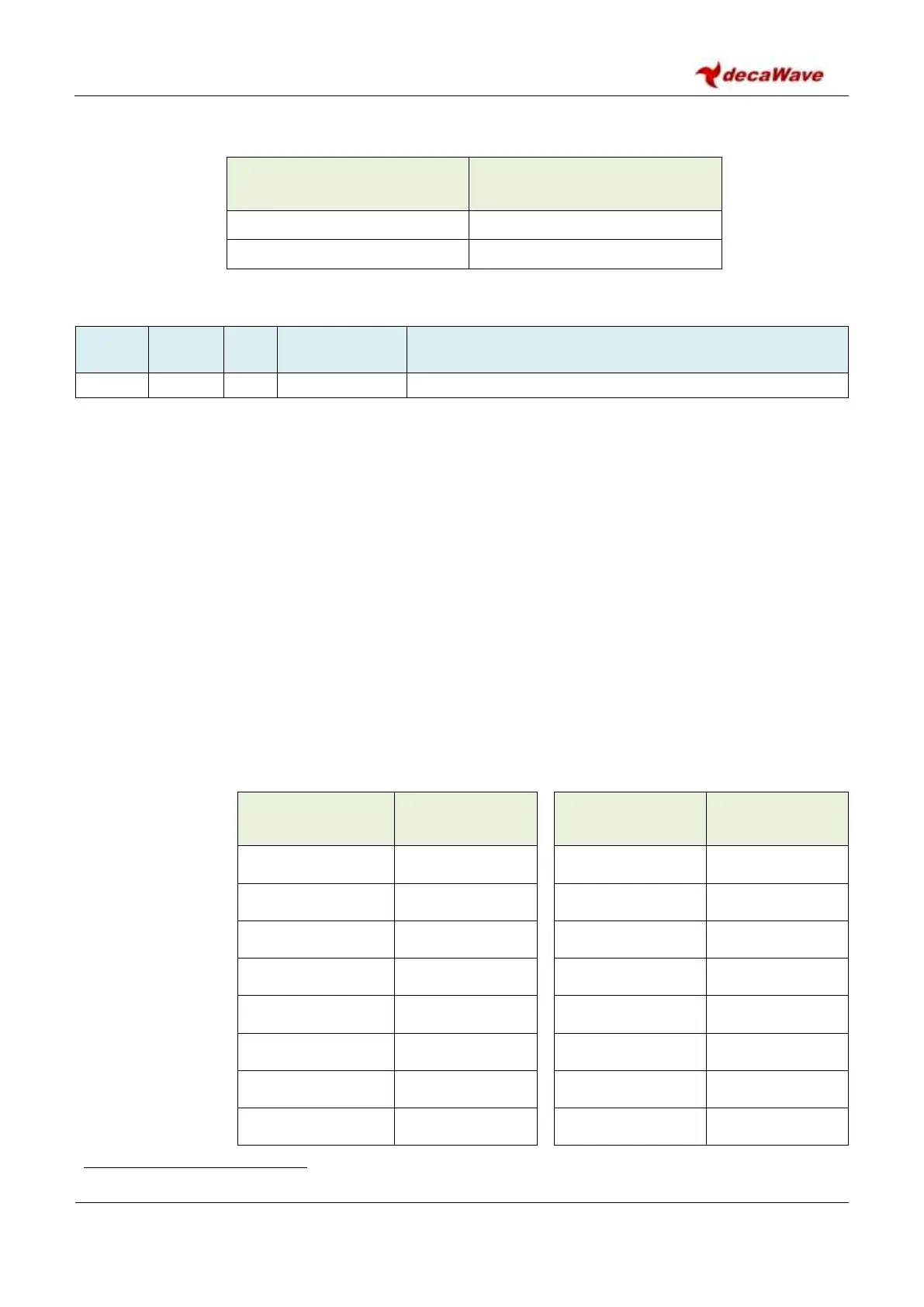

7.2.47.7 Sub-Register 0x2E:2804 – LDE_REPC

LDE Replica Coefficient configuration

Register file: 0x2E – Leading Edge Detection Interface, sub-register 0x2804 is a 16-bit configuration register

for setting the replica avoidance coefficient. The accumulator operates on the preamble sequence to give

the channel impulse response. This works because of the perfect periodic auto-correlation property of the

IEEE 802.15.4 UWB preamble sequences. The auto-correlation is not perfect where there is a significant

clock offset between the remote transmitter and the local receiver. In these circumstances small amplitude

replicas of the channel impulse response appear repeatedly throughout the accumulator span. The

magnitude of this effect is dependent on the clock offset and on the preamble code being employed. To

avoid the LDE erroneously seeing one of these replica signals as the leading edge the threshold used for

detecting the first path is artificially raised by a factor depending on the measured clock offset. For optimum

performance this factor also needs to be dependent on the preamble code selected in the receiver. To

achieve this, the LDE_REPC configuration needs to be set depending on the receiver preamble code

configuration. The values required are given in Table 51. These values apply to 850 kbps and 6.8 Mbps data

rates only.

Table 51: Sub-Register 0x2E:2804 – LDE_REPC configurations for (850 kbps & 6.8 Mbps)

9

RX_PCODE configuration is set Register file: 0x1F – Channel Control

Loading...

Loading...