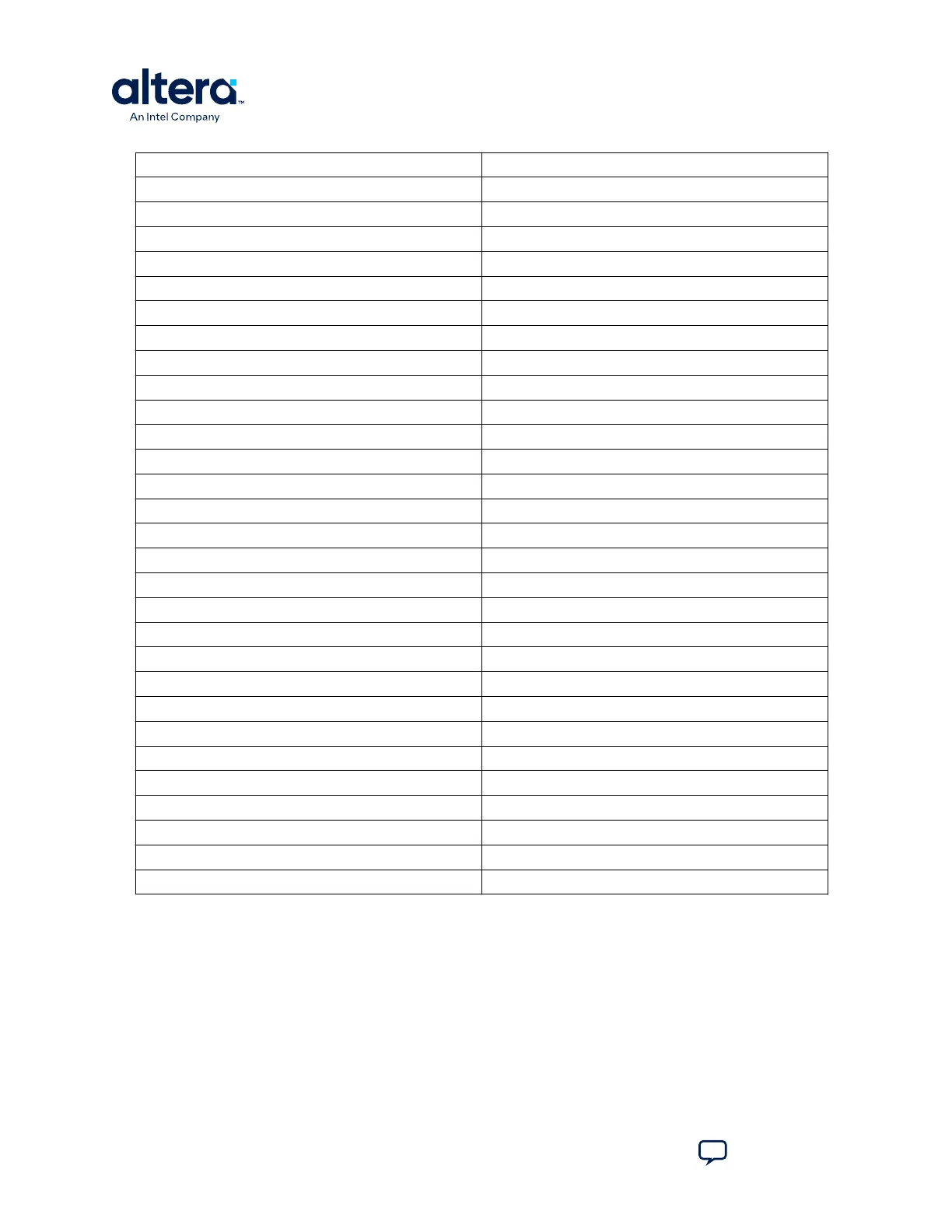

Schematic Signal Names Description

SFP2_RATE_SEL Module Rate Select 0

SFP2_MOD1_PRSNT_N Module Present

SFP2_LOS Loss of Signal

SFP2_TX_FAULT Transmitter Fault Indication

SFP2_RS1 Module rate select 1

SFP2_MOD1_SCL I

2

C clock

SFP2_MOD1_SDA I

2

C data

SFP2_TX_DP/DN Transceiver TX

SFP2_RX_DP/DN Transceiver RX

SFP1_TX_DISABLE Transmitter Disable

SFP1_RATE_SEL Module Rate Select 0

SFP1_MOD2_PRSNT_N Module Present

SFP1_LOS Loss of Signal

SFP1_TX_FAULT Transmitter Fault Indication

SFP1_RS1 Module rate select 1

SFP1_MOD2_SCL I

2

C clock

SFP1_MOD2_SDA I

2

C data

SFP1_TX_DP/DN Transceiver TX

SFP1_RX_DP/DN Transceiver RX

SFP0_TX_DISABLE Transmitter Disable

SFP0_RATE_SEL Module Rate Select 0

SFP0_MOD3_PRSNT_N Module Present

SFP0_LOS Loss of Signal

SFP0_TX_FAULT Transmitter Fault Indication

SFP0_RS1 Module rate select 1

SFP0_MOD3_SCL I

2

C clock

SFP0_MOD3_SDA I

2

C data

SFP0_TX_DP/DN Transceiver TX

SFP0_RX_DP/DN Transceiver RX

FMC + Connectors

Agilex 7 FPGA I-Series Transceiver Development Kit supports 2x FMC+ slots for

functional expandability. The x16 FGT lanes from bank 13C and 12A are terminated to

FMC-A (J7) and FMC-B (J9) connectors respectively. Auxiliary signals are controlled by

the System MAX 10.

A. Development Kit Components

776646 | 2024.11.21

Agilex

™

7 FPGA I-Series Transceiver (6 × F-Tile) Development Kit User Guide

Send Feedback

60

Loading...

Loading...