A HARDWARE REFERENCE

3-21

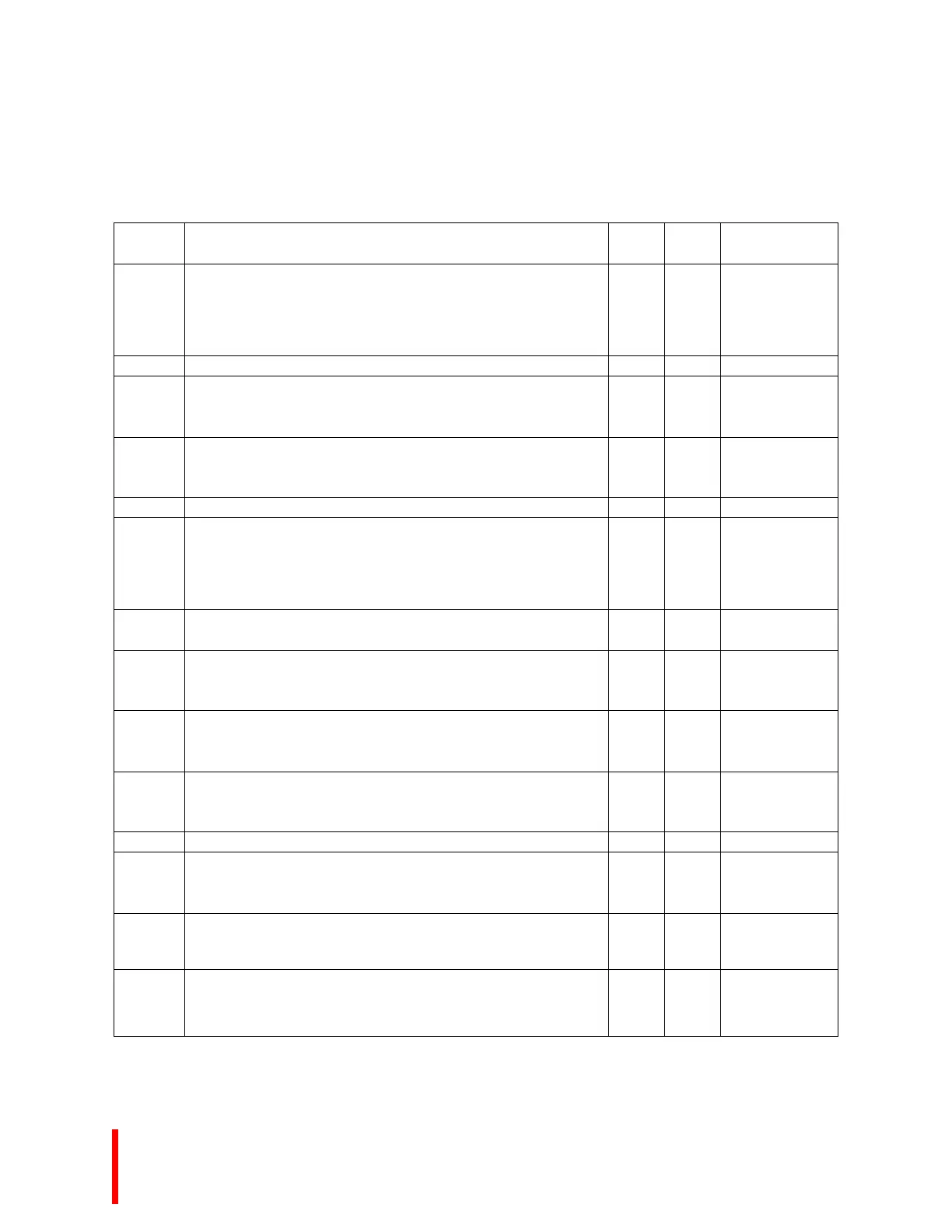

Table 3-24. Local Bus Region Descriptor for PCI-to-Local Access Register Description

Field Description Read Write

Value after Reset

(Cold PC Reset)

1:0

Memory Space 0 Local Bus Width:

00 indicates a bus width of 8 bits

01 indicates a bus width of 16 bits

10 or 11 indicates a bus width of 32 bits

Must be set to 11 (32 bit bus width)

Yes Yes 11

5:2 Memory Space 0 Internal Wait States. Must be 0. Yes Yes 0

6

Memory Space 0 READY Input Enable:

0 disables the READY input; 1 enables READY input.

Must be 1.

Yes Yes 0

7

Memory Space 0 BTERM Input Enable:

0 disables BTERM input; 1 enables BTERM input.

Must be 0.

Yes Yes 0

15:8 Not Used Yes Yes 0

17:16

Expansion ROM Space Local Bus Width:

00 indicates a bus width of 8 bits;

01 indicates a bus width of 16 bits;

10 or 11 indicates a bus width of 32 bits

Must be 00 - expansion flash is 8 bits wide on the PCI-SDK Platform.

Yes Yes 11

21:18

Expansion ROM Space Internal Wait States.

Must be 0.

Yes Yes 0

22

Expansion ROM Space READY Input Enable:

0 disables READY input; 1 enables READY input.

Must be 1.

Yes Yes 0

23

Expansion ROM Space BTERM Input Enable:

0 disables BTERM input; 1 enables BTERM input.

Must be 0.

Yes Yes 0

24

Memory Space 0 Burst Enable:

0 disables bursting; 1 enables bursting.

Must be 1.

Yes Yes 0

25 Not Used Yes Yes 0

26

Expansion ROM Space Burst Enable:

0 disables bursting; 1 enables bursting.

Must be 0.

Yes Yes 0

27

Direct Slave PCI write mode.

0 - PCI 9060 disconnects when the Direct Slave write FIFO is full.

1 - PCI 9060 de-asserts TRDY when the write FIFO is full.

Yes Yes 0

31:28

PCI Target Retry Delay Clocks. Contains the value (multiplied by 8) of the

number of PCI bus clocks after receiving a PCI-Local read or write access

and not successfully completing a transfer. Only pertains to Direct Slave

writes when bit 27 is set to 1.

Yes Yes

4

(32 clocks)

Loading...

Loading...