A SQUALL II MODULE INTERFACE

5-5

5.5 Squall Module Signal Descriptions

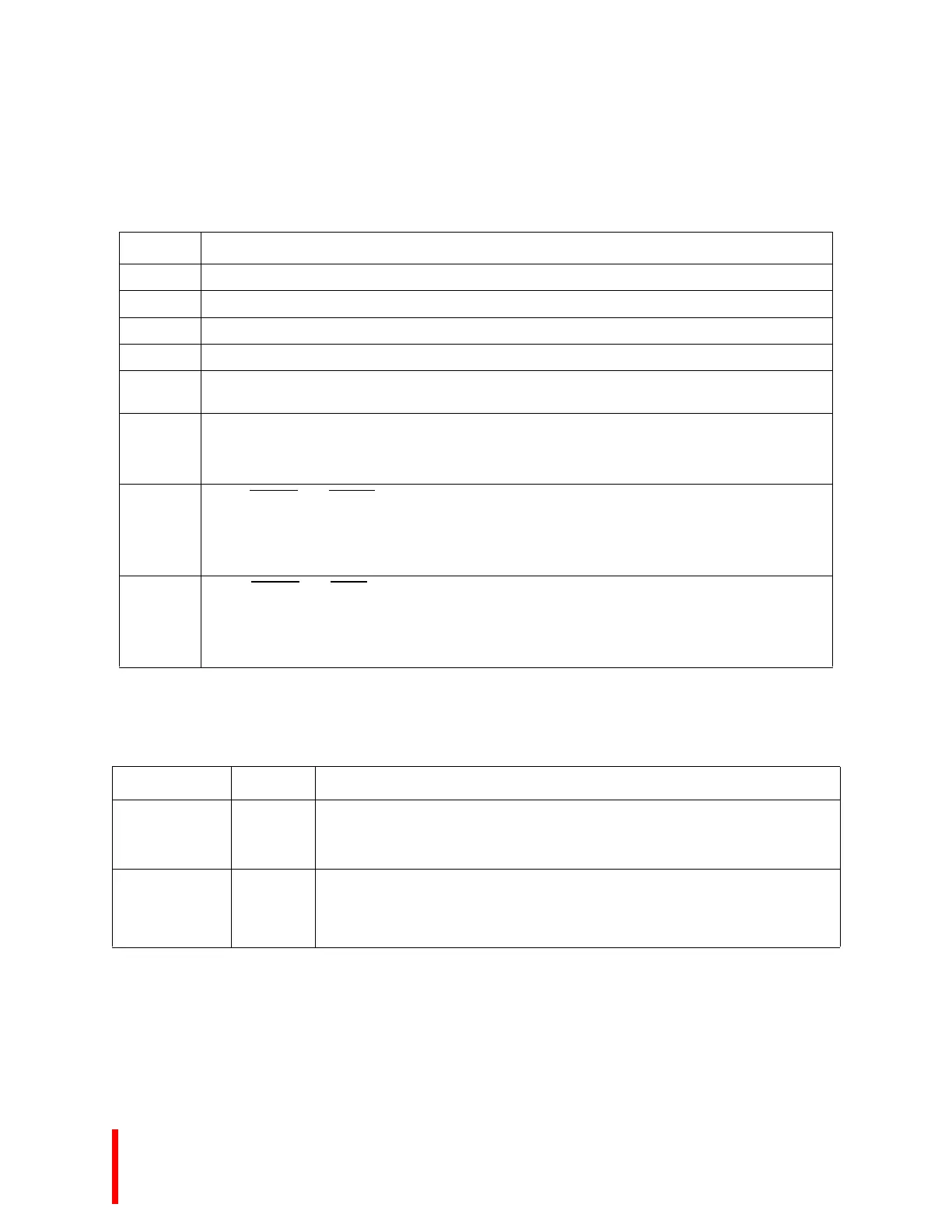

Table 5-2. Pin Description Nomenclature

Symbol Description

I Input only pin

O Output only pin

I/O Pin may be either an input or output

- Pin must be connected as described

S Synchronous. Inputs are synchronous to PMCLK. Outputs must meet setup and hold times relative

to PMCLK.

A( ) Asynchronous. Outputs may be asynchronous to PMCLK.

A(E) Edge Sensitive Output

A(L) Level Sensitive Output

SL( ) While EHOLD

and EHLDA are inactive, the pin functions in the slave mode.

SL(O) Output

SL(I) Input

SL(I/O) As an input or an output

M( ) When EHOLD

and HLDA are asserted, the module is in master mode.

M(I) Input

M(O) Output

M(I/O) As an input or output

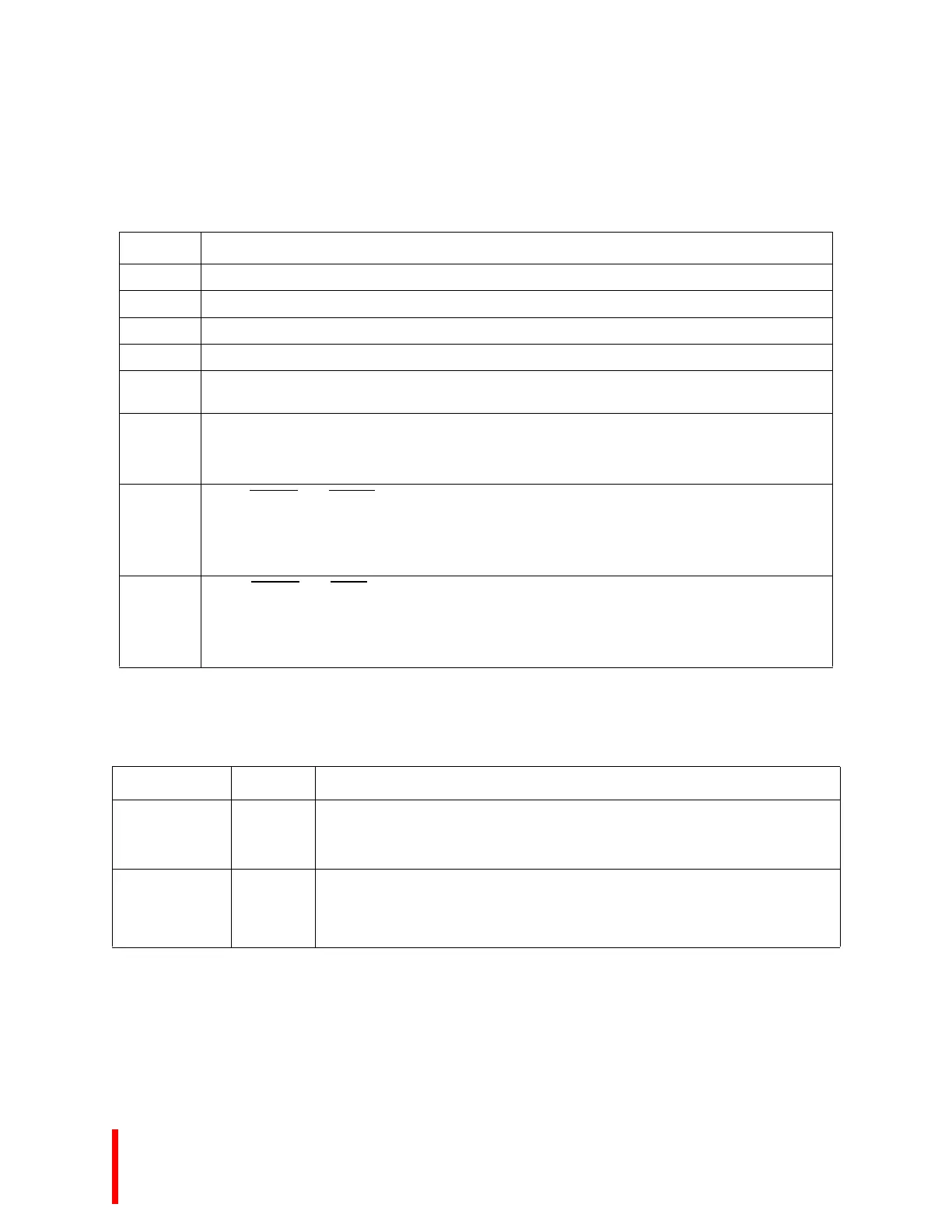

Table 5-3. Squall Module Signal Descriptions (Sheet 1 of 3)

Name Type Description

S_A[02:31]

SL(I)

M(O)

S

Address Bus carries the upper 30 bits of address. The byte enable signals indicate

the selected byte in each word.

S_D[00:31]

I/O

S

Data Bus carries 32, 16, or 8 bit data depending on the bus width configured in the

Memory Region Table. For a bus width of 8 bits, data lines D[00:07] are used. For

16 bits, D[00:15] are used. For 32 bits, the full bus is used. In master mode, all

transfers with the memory use full data bus.

Loading...

Loading...