PPC600 Family Debugger | 15

©

1989-2022 Lauterbach

Software Breakpoint Handling

For software breakpoint functionality, the debugger must set an on-chip breakpoint to the program interrupt

address. As PPC603-based cores have two possible interrupt addresses based on MSR[IP].

In situations where there are less than two on-chip breakpoints available there is a resource conflict. The

unavailability can be caused by CPU design, or if the user makes direct use of on-chip breakpoints.

If the source code modifies MSR[IP], then a manual correction is necessary to use the correct exception

handler.

Following some logic structure examples to explain this special situations.

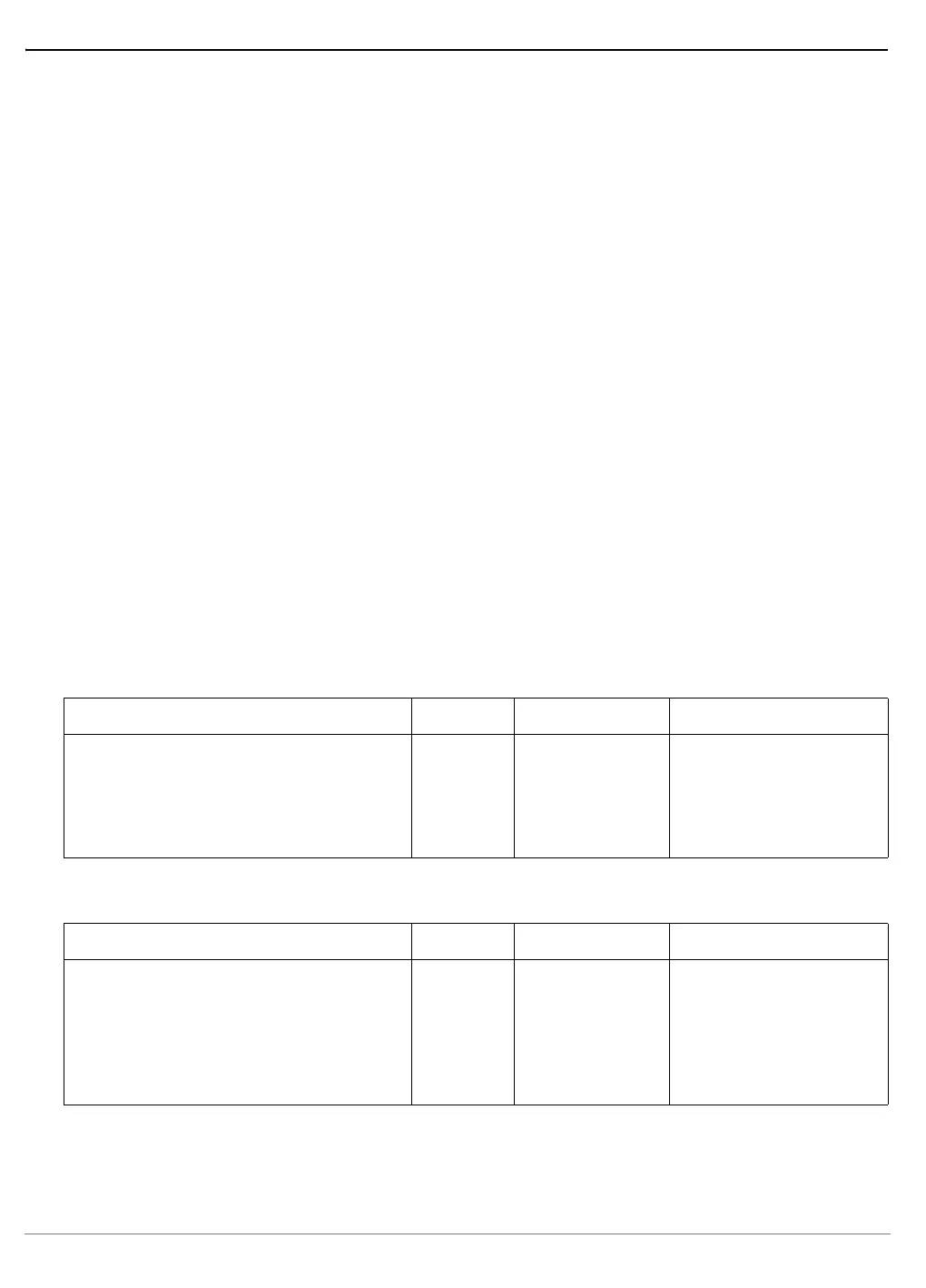

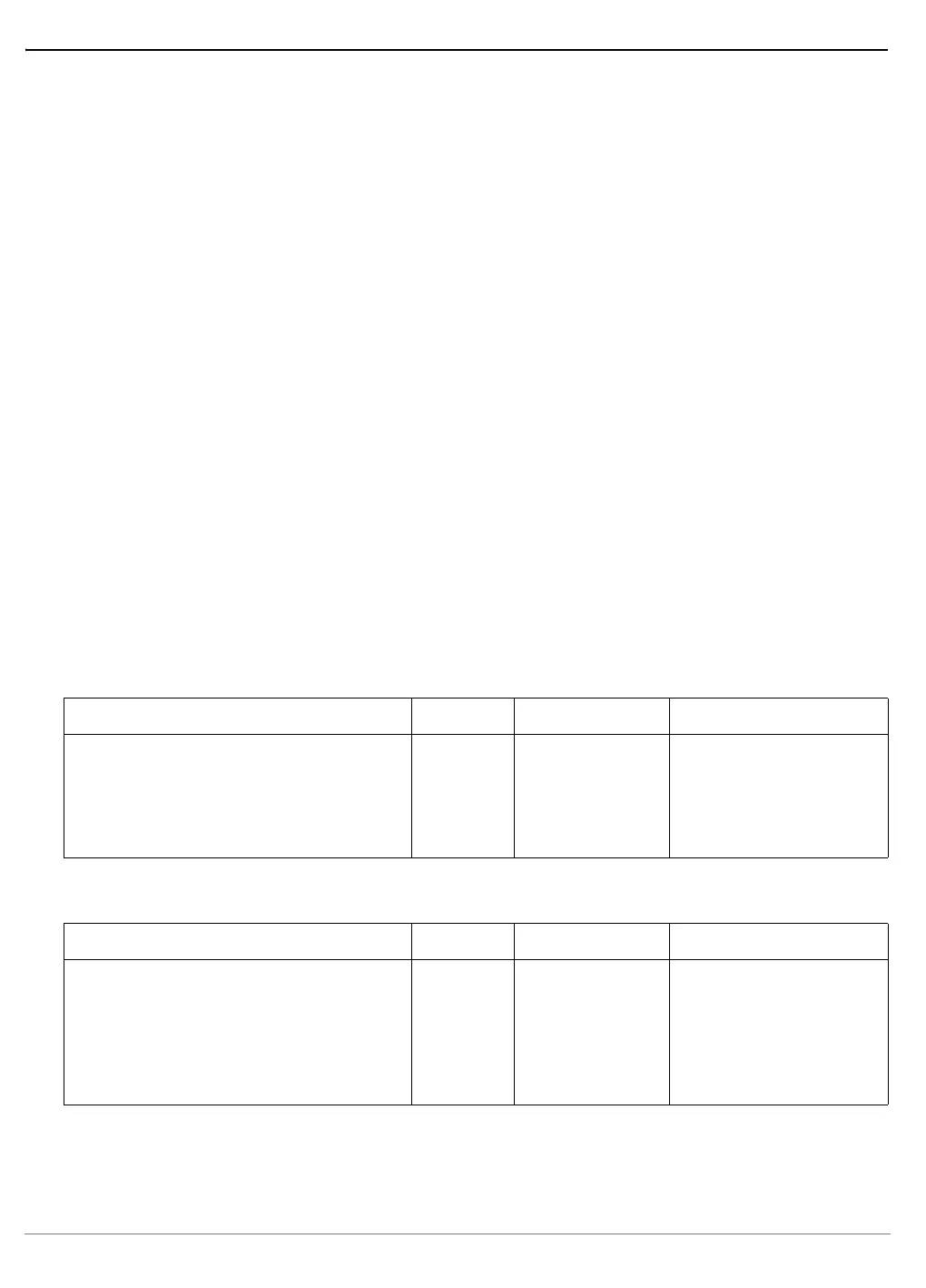

Source code structure for all modes:

AUTO-Mode:

Manual-Mode 0/1

0x00

0x04

0x08

0x0C

0x10

0x14

0x18

0x1C

0x20

…

code

code

1. SW-BP

code

code

code change MSR[IP] bit to 0

code

2. SW-BP

code

…

Command Sequence / CPU Status MSR[IP] Exception Pos Comment

CPU is stopped, PC at 0x00

go

CPU stop at 0x08

go

CPU is still running

1

1

1

1/0

0

1

1

1

1

1

Break OK.

Break error!

Command Sequence / CPU Status MSR[IP] Exception Pos Comment

CPU is stopped, PC at 0x00

go

CPU stop at 0x08

set sys.option.ip 0

go

CPU stop at 0x1C

1

1

1

1

1/0

0

1

1

1

0

0

0

Break OK.

Break OK.

Loading...

Loading...