HAP-S1

HAP-S1

5050

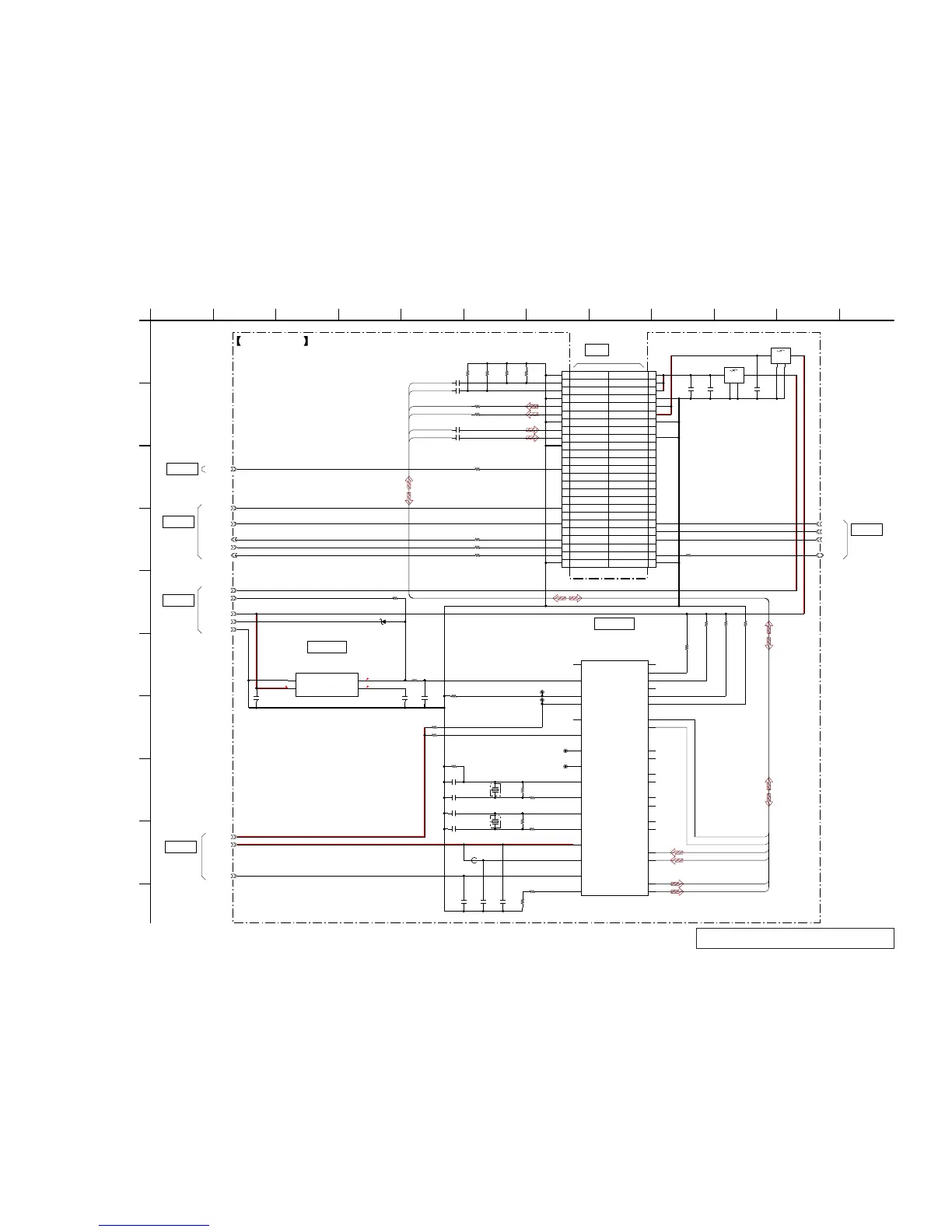

See page 78 for IC Block Diagrams. • See page 86 for IC Pin Function Description.

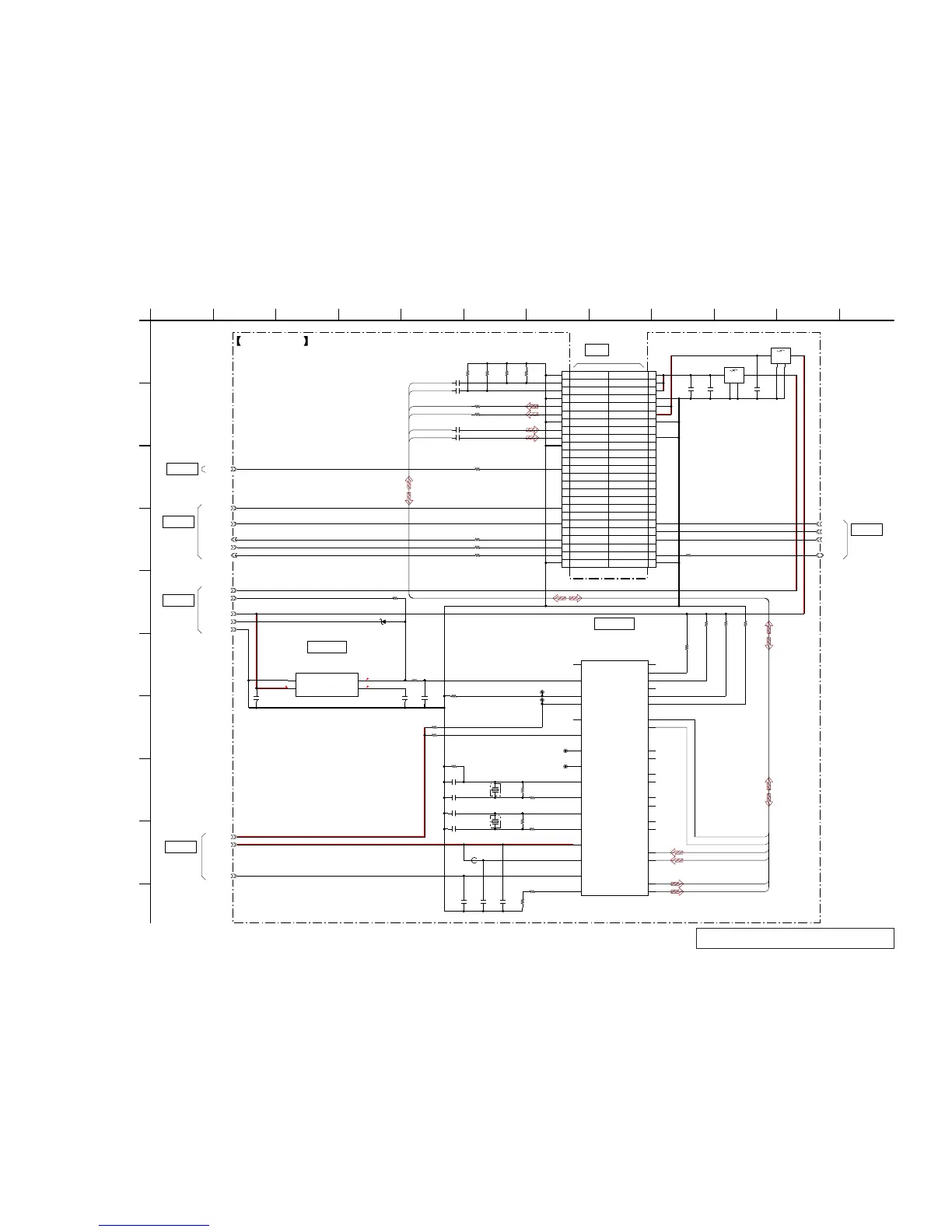

5-10. SCHEMATIC DIAGRAM - MAIN Section (4/9) -

Note: IC101 on the MAIN board cannot exchange with single. When

this part is damaged, exchange the complete mounted board.

3.3

3.3

1.6

PST8429UL

IC401

GND

1

VDD

2

CD

3

OUT

4

0

R410

0

R411

10k

R413

10k

R422

10k

R418

10k

R417

10M

R409

2.2M

R404

0.047

C402

3.3k

R406

0.01

C401

10M

R425

4.7k

R426

0.22

C407

PCIE_2.5V

0.22

C409

PCIE_1.1V

0.22

C408

100

R429

100

R430

FB401

CL401

CL402

RESET_MPU_B

50P

CN402

1GND 25V

3 PCIE_REFCLK_N 45V

5 PCIE_REFCLK_P 65V

7GND 8GND

9 PCIE_TX_N 103.3V

11 PCIE_TX_P 123.3V

13 GND 14GND

15 PCIE_RX_N 16IMX_MCLK

17 PCIE_RX_P 18GND

19 GND 20IMX_BCLK

21 W_DISABLE#(4_14) 22IMX_LRCLK

23 PCIE_WAKE#(5_20) 24IMX_SDOUT

25

PCIE_PERSTN(7_12)

26IMX_SDIN

27

PCIE_PWR_EN(3_19)

28IMX_BCLK2(1_12)

29 FPGA_DATA(7_13) 30IMX_LRCLK2(1_14)

31 CS_DSP(2_26) 32IMX_SDOUT2(1_13)

33 NC(2_27) 34IMX_SDIN2(1_15)

35 SDO_DSP(2_24) 36

EPCS_NCS_IMX6(1_11)

37 SDI_DSP(2_25) 38

EPCS_ASDI_IMX6(1_10)

39 SDK_DSP(2_23) 40

FPGA_CONF_DONE(5_18)

41 FPGA_DCLK(4_10) 42FPGA_RST(5_19)

43

FPGA_INTERRUPT(5_2)

44FPGA_EN(5_21)

45

FPGA_NCONFIG(3_20)

46HOLD_FLASH(5_27)

47

FPGA_NSTATUS(3_23)

48

FPGA_INIT_DONE(5_26)

49 GND 50GND

0.1

C410

0.1

C411

0

R431

0

R432

0.1

C412

0.1

C413

PCIE_RST

I2C1_SDA

0

R456

0

R457

0

R458

GPIO5_[18]

GPIO5_[19]

GPIO5_[21]

24MHz

X401

0.1

C415

10

C416

0.1

C417

GPIO5_[2]

GPIO3_[20]

GPIO3_[23]

0

R454

0

R466

32.768kHz

X403

0

R468

0

R469

3.3V

SNVS3.3V

GND

5V

CL403

CL404

100

R470

100

R471

100

R472

100

R473

FL400

OUT

GND1

IN

GND2

FL401

OUT

GND1

IN

GND2

NSR0320MW2T1G

D403

CSPI2_SCLK

CSPI2_MOSI

STANDBY3.3V

MCIMX6D5EYM10AC

IC101

ONOFF

D12

POR_B

C11

BOOT_MODE0

C12

BOOT_MODE1

F12

TEST_MODE

E12

TAMPER

E11

PMIC_STBY_REQ

F11

PMIC_ON_REQ

D11

XTALI

A7

XTALO

B7

RTC_XTALI

D9

RTC_XTALO

C9

PCIE_VP

H7

PCIE_VPTX

G8

PCIE_VPH

G7

PCIE_REXT

A2

JTAG_TCK

H5

JTAG_TMS

C3

JTAG_TDI

G5

JTAG_TDO

G6

JTAG_TRSTB

C2

JTAG_MOD

H6

CLK1_N

C7

CLK1_P

D7

CLK2_N

C5

CLK2_P

D5

MLB_CP

B11

MLB_CN

A11

MLB_SP

B9

MLB_SN

A9

MLB_DP

A10

MLB_DN

B10

PCIE_RXM

B1

PCIE_RXP

B2

PCIE_TXM

A3

PCIE_TXP

B3

6p

C403

6p

C404

18p

C406

22p

C405

100

R463

0.01

C418

CLK1_N

CLK1_P

PCIE_TXM

PCIE_TXP

PCIE_RXM

PCIE_RXP

CLK1_N

CLK1_P

PCIE_RXM

PCIE_RXP

PCIE_TXM

PCIE_TXP

IC401

RESET SIGNAL GENERATOR

>03S

(2/3)

CN401

BOARD

FPGA DSP

(Chip Size Package)

(5/10)IC101

MPU

CSP

>102S

(1/9)

BOARD

MAIN

>106S

(2/9)

BOARD

MAIN

>115S

(8/9)

BOARD

MAIN

>114S

(5/9)

BOARD

MAIN

>116S

(7/9)

BOARD

MAIN

G

H

I

F

2

B

3

A

451

J

6789101112

C

D

E

(4/9)MAIN BOARD

(Page 53)

(Page 51)

(Page 54)

(Page 48)

(Page 47)

(Page 60)

Loading...

Loading...