HAP-S1

HAP-S1

6161

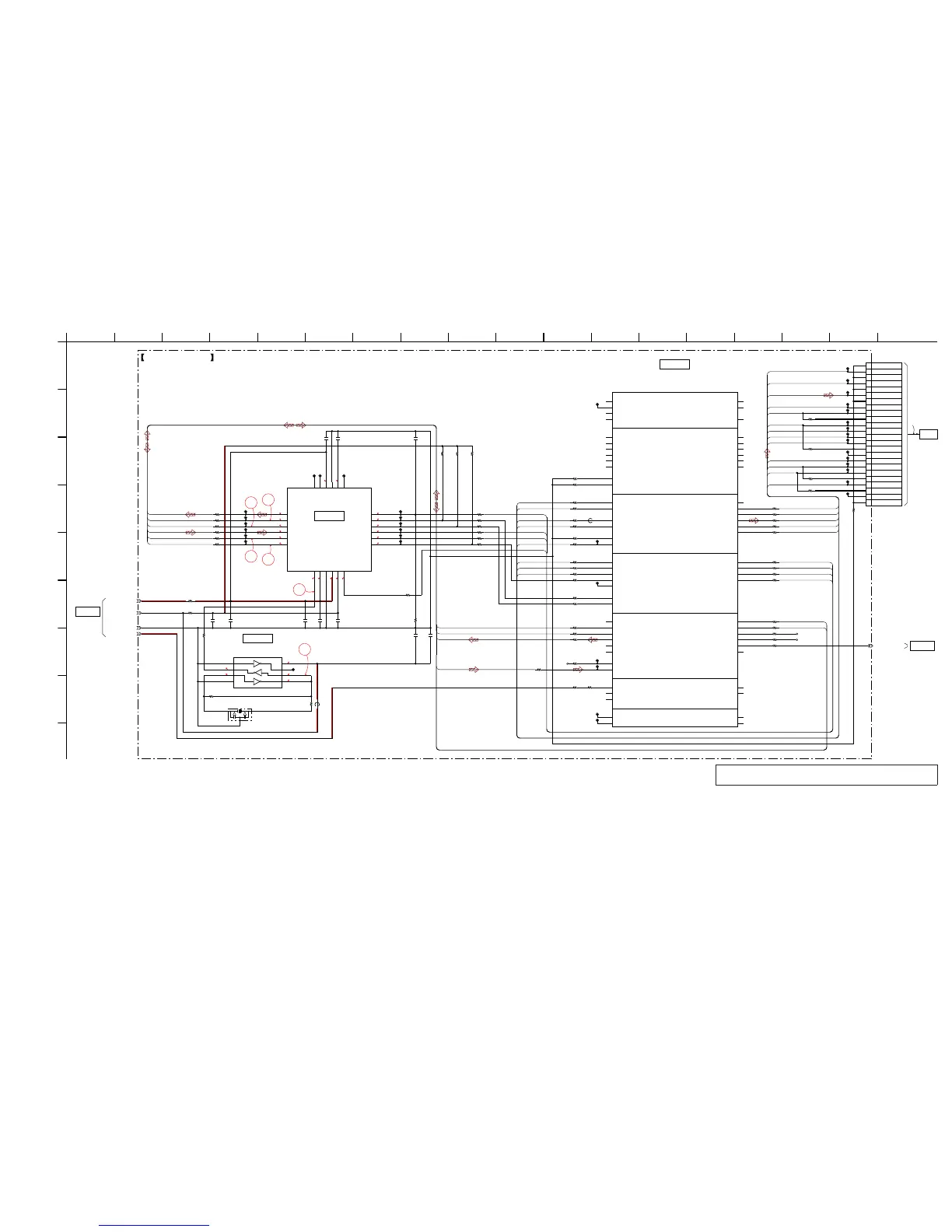

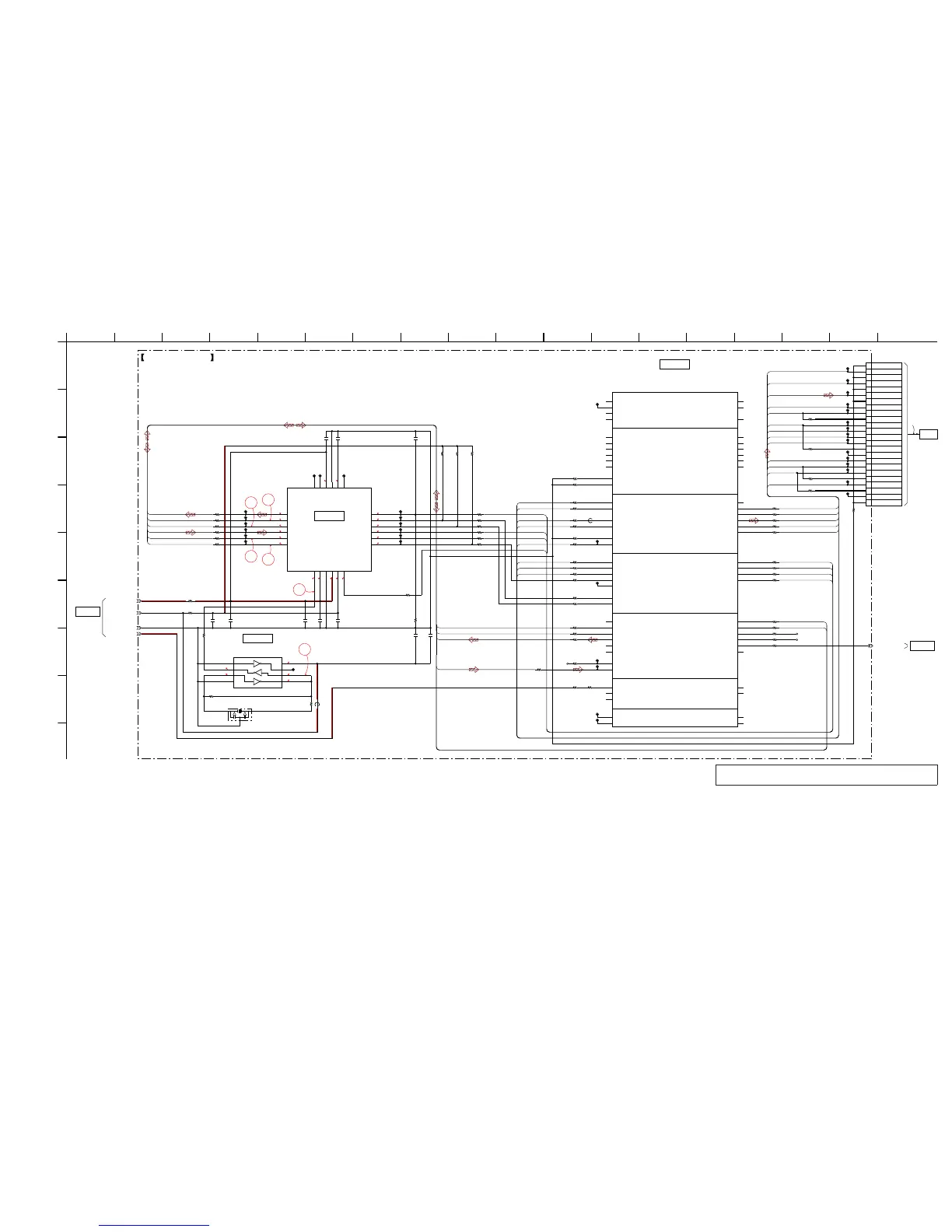

• See page 73 for Waveforms. • See page 86 for IC Pin Function Description.

5-21. SCHEMATIC DIAGRAM - FPGA DSP Board (3/3) -

Note: IC001 and IC702 on the FPGA DSP board cannot exchange with single.

When these parts are damaged, exchange the complete mounted board.

1.2

3.3

3

3.2

3.2

0

3.2

3.2

0

3.3

1.2

1.2

1.6

0

1.6

1.6

0

1.6

1.6

1.6

1.5

3.3

1.6

1.6

26

25

24

23

22

21

10

R528

10

R526

10R527

10

R522

10

R520

10

R519

10R521

10R550

10R552

10

R532

220

R514

10R556

10

R554

100

R549

10R555

CL503

CL504

10

R531

100

R515

10

R553

10

R557

R518

820

10

R523

10

R524

10

R558

10

R559

10

R560

10

R561

10

R562

FPGA_INTERRUPT

R534

10

100R551

10

R512

10R513

CL501

CL502

R570

10k

24P

CN506

1 DIRGND

2L

3 DIRGND

4BCLK_L

5 DIRGND

6 DATA_DSDL

7 DIRGND

8 LRCLK_DSDR

9AMUTE

10 CTRLGND

11 RESET

12 MC

13 MDI

14 ZMS

15 CTRLGND

16 DSD128_XDSD64

17 DSD_XPCM

18 24M_OE

19 22M_OE

20 CLKGND

21 FS128IN

22 CLKGND

23 FS512IN

24 CLKGND

R575

0

2.2k

R576

CL505

CL506

CL507

CL508

CL509

CL510

CL511

CL512

CL513

CL514

CL515

CL516

CL517

CL518

CL519

2.2k

R577

2.2k

R578

2.2k

R579

FB501

10k

R580

10k

R581

10k

R582

VDD_3.3V

CL520

CL521

CL522

BANK 3

BANK 4

BANK 5

BANK 6

BANK 7

BANK 8

BANK 9

EP4CGX30BF14C8N

IC001

IO/DIFFIO_B1P/CRC_ERROR

N4

IO/DIFFIO_B1N/NCEO

N5

IO/DQS1B/CQ0B#/DPCLK2

L5

IO/VREFB3N0

L7

IO/DIFFIO_B12P/DQ0B

N8

IO/DIFFIO_B12N/DQ0B

N9

IO/VREFB4N0

K8

IO/DQ0B

K9

IO/RUP2/DQ0B

M11

IO/RDN2/DM0B

N12

CLK14/DIFFCLK_6P

M7

CLK15/DIFFCLK_6N

N7

IO/DQS1R/CQ0R#/DPCLK7

H10

IO/VREFB5N0

H12

IO/RUP3

N13

IO/RDN3

M13

CLK5/DIFFCLK_2P

H13

CLK4/DIFFCLK_2N

G13

IO/DIFFIO_R2P

D11

IO/DIFFIO_R2N

D12

IO/DIFFIO_R4P/DM0R

E10

IO_F9

F9

IO/VREFB6N0

E13

CLK7/DIFFCLK_3P

F12

CLK6/DIFFCLK_3N

F13

IO/DIFFIO_T11P/DM0T

A12

IO/DIFFIO_T11N/DQ0T

A11

IO_B11

B11

IO/VREFB7N0

B10

IO/RUP4/DQ0T

C11

IO/RDN4/DQ0T

C12

CLK9/DIFFCLK_5P

A10

CLK8/DIFFCLK_5N

A9

IO/CLKUSR

A6

IO/DQS1T/CQ0T#/DPCLK13

B6

IO/VREFB8N0

C6

IO/NCSO

C5

IO/ASDO

B5

IO/PLL1_CLKOUTP

L4

IO/PLL1_CLKOUTN

M4

IO/DIFFIO_B3N/DQ0B

N6

IO/PLL3_CLKOUTP

K10

IO/PLL3_CLKOUTN

L11

IO/DIFFIO_B19P/DQ0B

L9

IO/DIFFIO_B19N/DQS0B/CQ0B/DPCLK5

M9

IO/DIFFIO_B21P/DQ0B

N10

IO/DIFFIO_B21N/DQ0B

N11

IO/DIFFIO_R9N/DQ0R

J13

IO/DIFFIO_R9P/DQ0R

K13

IO/DIFFIO_R13P/DQ0R

L12

IO/DIFFIO_R13N/DQ0R

L13

IO/DIFFIO_R14P/DQ0R

K11

IO/DIFFIO_R14N/DQ0R

K12

IO/DIFFIO_R5P/DQ0R

F10

IO/DIFFIO_R5N/DQ0R

F11

IO/DIFFIO_R6P/DQS0R/CQ0R/DPCLK8

G9

IO/DIFFIO_R6N/DEV_OE

G10

IO/DIFFIO_T12P/DQ0T

C8

IO/DIFFIO_T12N/DQ0T

B8

IO/DIFFIO_T17P/DQ0T

B13

IO/DIFFIO_T17N/DQS0T/CQ0T/DPCLK10

A13

IO/DIFFIO_T18P/DQ0T

D13

IO/DIFFIO_T18N/DQ0T

C13

IO/PLL2_CLKOUTP

A8

IO/PLL2_CLKOUTN

A7

NC_N2

N2

NC_M3

M3

SDI_DSP

SDK_DSP

RST_DSP

128FS_IN

SDI_DSP

SDO_DSP

LRCLK_OUT_CIRRUS

BCLK_OUT_CIRRUS

WDCKL_DSDL

DSD_XPCM

22M_OE

WDCKR_DSDR

SDK_DAC

DATAL_DSDLD

RST_DSP

CS_DAC

SDK_DSP

SDO_DAC

22M_OE

24M_OE

DATAR_DSDRD

AMUTE

RST_DAC

DSD_XPCM

WDCKR_DSDR

24M_OE

WDCKL_DSDL

AMUTE

SDK_DAC

SDO_DAC

CS_DAC

DATAR_DSDRD

DATAL_DSDLD

RST_DAC

SDO_DSP

128FS_IN

FPGA

IC001

CSP

(Chip Size Package)

(4/4)

FFC2

DIGITAL IO

BOARD

>11S

CN4006

FPGA DSP

>135S

(2/3)

BOARD

CS48L10-CNZR

IC702

CLOCK

1

VPLL

2

GND_3

3

VD_4

4

VL_5

5

CLK/SCL

6

nCS

7

MISO/SDA

8

MOSI

9

nBUSY/HS0/nEE_CS

10

nINT/HS1

11

nRESET

12

DBCK

13

VL_14

14

GND_15

15

VD_16

16

DBDA

17

MCLK

18

DAO_D1

19

DAO_LRCLK

20

DAO_SCLK

21

DAI_D1

22

DAI_LRCLK

23

DAI_SCLK

24

R703

10

R704

10

R705

10

R706

10

R707

10

R708

10

CIRRUS_CORE_1.2V

CIRRUS_3.3V

C703

0.1

C705

0.1

C708

0.1

R702

0

R701

0

C704

0.1

C707

0.1

C710

0.01

R723 22

R724 22

R725 22

R722 22

R719

22

R721 22

CL710

CL708

CL701

CL702

CL703

CL704

CL705

CL706

CL707

CL711

CL712

CL713

CL714

CL715

CL716

C706

0.01

R709

22

IC701

TC7WHU04FK

1

2

3

GND

45

6

7

VCC

8

R712

3.3k

X701

6MHz

CL709

FB701

C709

0.1

R710

1M

R720

100

R714

10k

R716

10k

R718

10k

R713

2.2k

C701

10

C702

10

GND

BCLK_OUT

LRCLK_OUT

DATA_OUT

DATA_IN_CIRRUS

LRCLK_OUT_CIRRUS

BCLK_OUT_CIRRUS

BCLK_OUT

LRCLK_OUT

DATA_OUT

DATA_IN_CIRRUS

CLOCK BUFFER

IC701

AUDIO DSP

IC702

FPGA DSP

>132S

(1/3)

BOARD

1311 16

A

3 171086

I

E

2 9

G

D

5

B

C

7

F

14 15 181412

H

(3/3)FPGA DSP BOARD

(Page 59)

(Page 60)

(Page 57)

Loading...

Loading...