data at that address is F4, the following error message is

displayed on the crt:

ACQ_MEM : even @ 4008 FO < > F4

Maintenance—2230 Service

PRC. This test checks the Post Record Counter write

and the B-TRIG read circuitry. Twenty four unique

patterns are written into the Post Record Counter (U4115

U4116 and U4117) and read through the B Delay Timer

(U4123 U4124).

The B Delay Timer is clocked by a write to the Time

Base Divider register (U4114 pin 8 through U4107 pin 4),

the inactive B-GATE (U4121B pin 11), and the TRGD

(U4121B pin 13) signals.

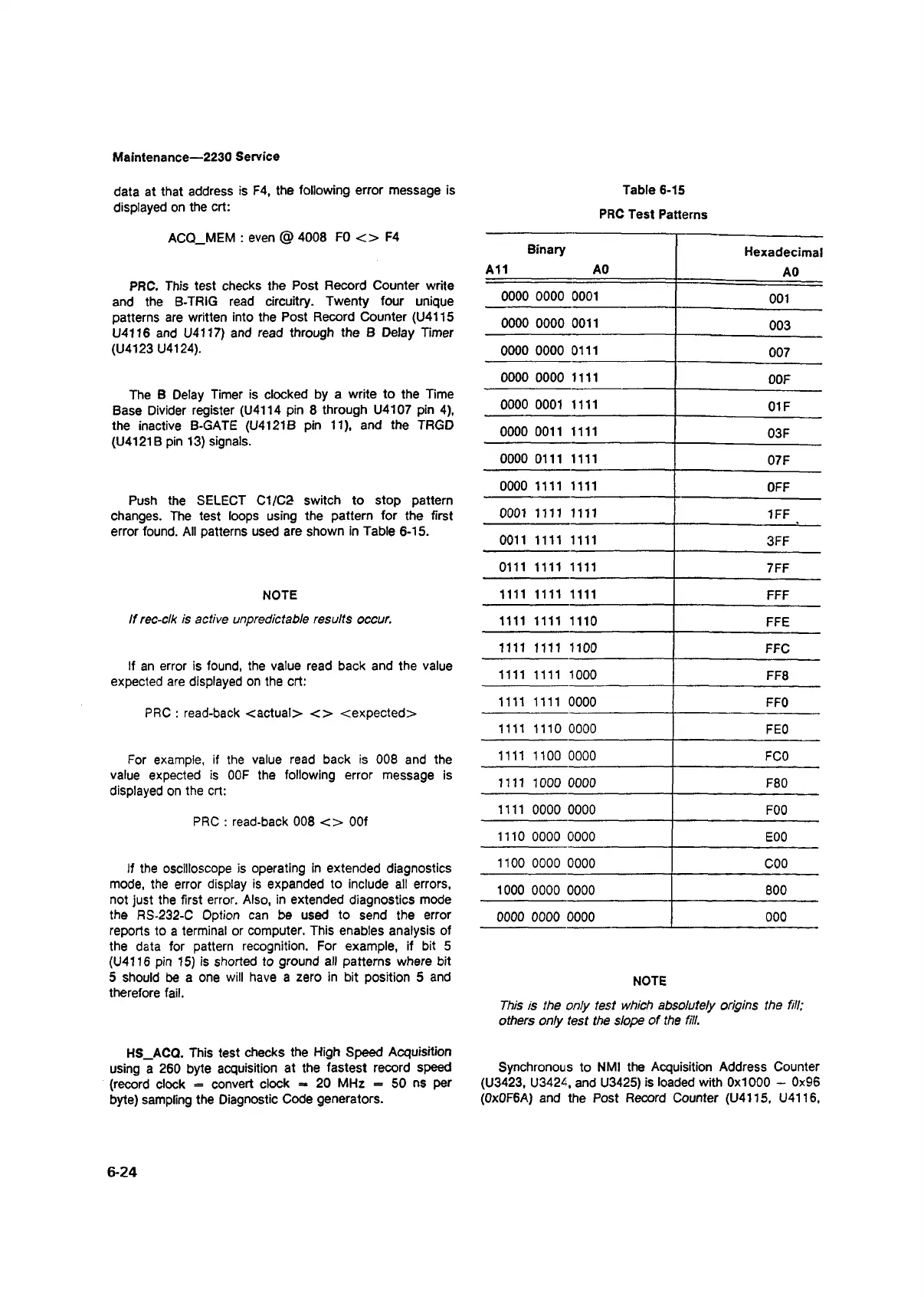

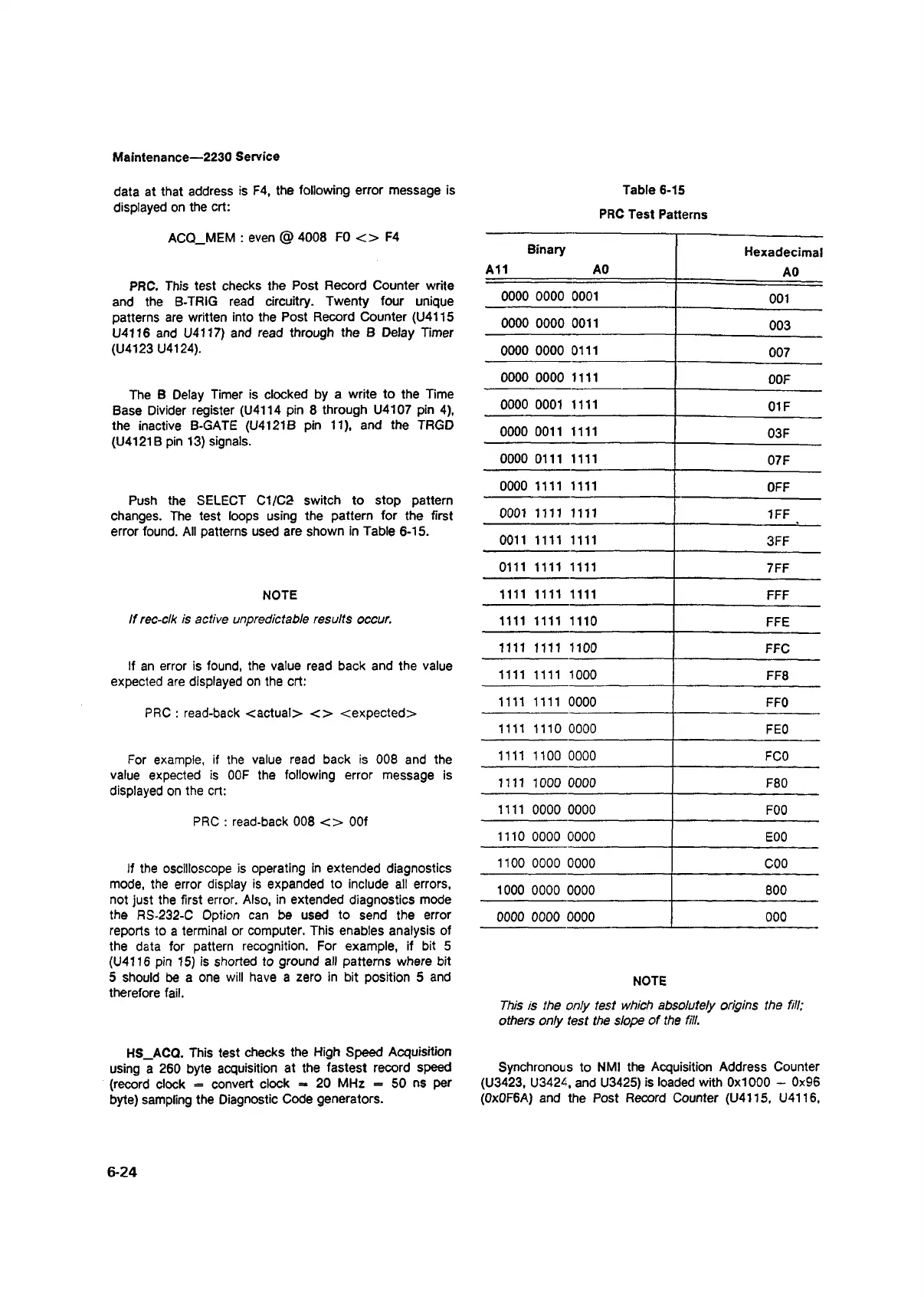

Push the SELECT C1/C2 switch to stop pattern

changes. The test loops using the pattern for the first

error found. All patterns used are shown in Table 6-15.

NOTE

If rec-clk is active unpredictable results occur.

If an error is found, the value read back and the value

expected are displayed on the crt:

PRC : read-back <actual> < > <expected>

For example, if the value read back is 008 and the

value expected is OOF the following error message is

displayed on the crt:

PRC : read-back 008 < > OOf

If the oscilloscope is operating in extended diagnostics

mode, the error display is expanded to include all errors,

not just the first error. Also, in extended diagnostics mode

the RS-232-C Option can be used to send the error

reports to a terminal or computer. This enables analysis of

the data for pattern recognition. For example, if bit 5

(U4116 pin 15) is shorted to ground all patterns where bit

5 should be a one will have a zero in bit position 5 and

therefore fail.

HS_ACQ. This test checks the High Speed Acquisition

using a 260 byte acquisition at the fastest record speed

(record clock = convert clock =* 20 MHz = 50 ns per

byte) sampling the Diagnostic Code generators.

Table 6-15

PRC Test Patterns

Binary

A ll A0

Hexadecimal

A0

0000 0000 0001

001

0000 0000 0011

003

0000 0000 0111

007

0000 0000 1111

OOF

0000 0001 1111

01F

0000 0011 1111

03F

0000 0111 1111

07 F

0000 1111 1111

OFF

0001 1111 1111

IFF

0011 1111 1111

3FF

0111 1111 1111

7FF

1111 1111 1111

FFF

1111 1111 1110

FFE

1111 1111 1100

FFC

1111 1111 1000

FF8

1111 1111 0000

FF0

1111 1110 0000

FE0

1111 1100 0000

FC0

1111 1000 0000

F80

1111 0000 0000

F00

1110 0000 0000

E00

1100 0000 0000

COO

1000 0000 0000 800

0000 0000 0000 000

NOTE

This is the only test which absolutely origins the fill;

others only test the slope of the fill.

Synchronous to NMI the Acquisition Address Counter

(U3423, U3424, and U3425) is loaded with 0x1000 - 0x96

(Ox0F6A) and the Post Record Counter (U4115, U4116,

6-24

Loading...

Loading...