114

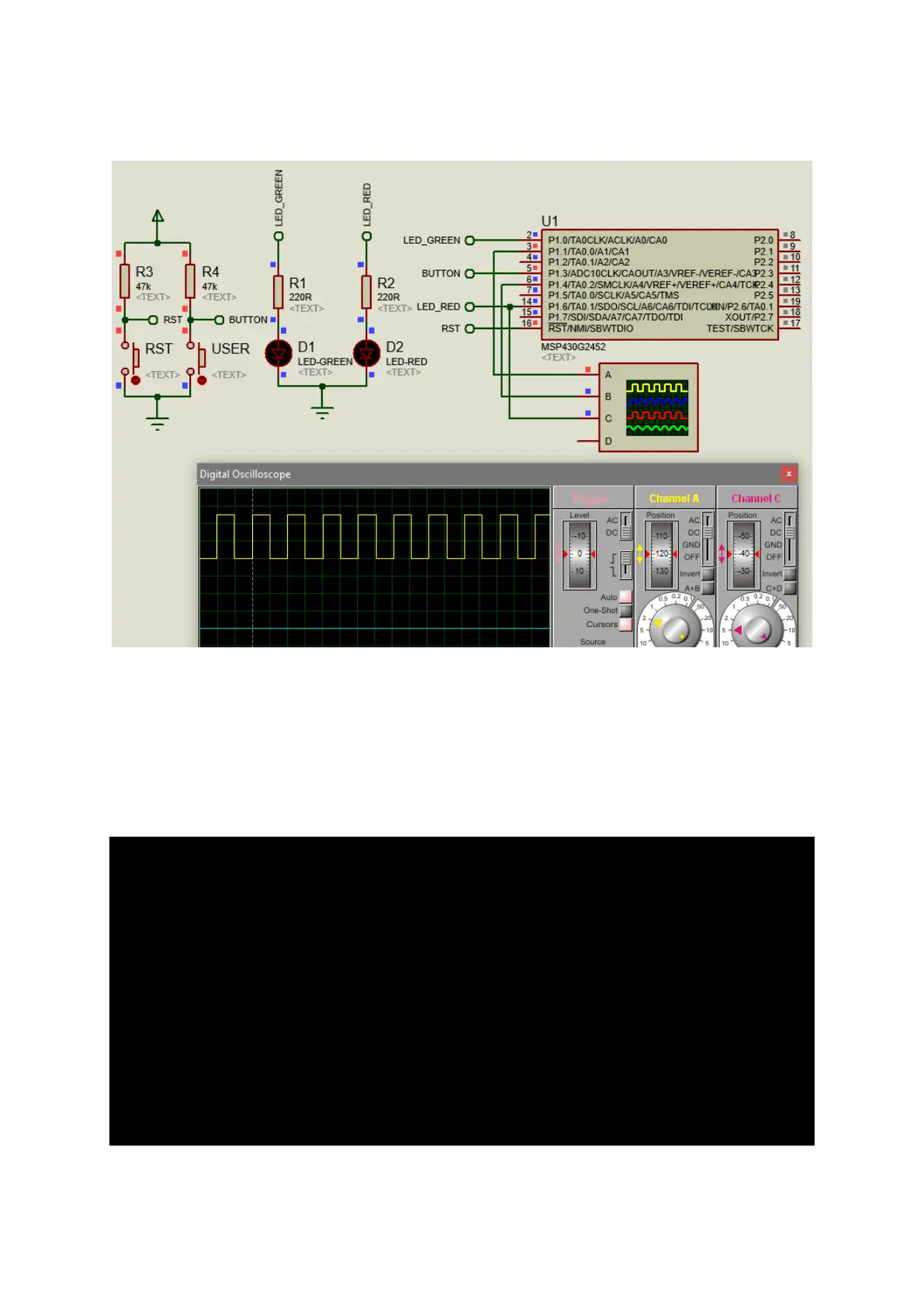

Simulation

Explanation

Just as in the previous example, SMCLK is set to 1MHz. Timer_A3 is also setup for up counting with a

top value of 999, resulting in 1ms time duration. Note no interrupt is used and other CCR registers are

loaded with 10 – an arbitrary value.

/* TA0CCR0, Timer_A Capture/Compare Register 0 */

TA0CCR0 = 999;

/* TA0CCR1, Timer_A Capture/Compare Register 1 */

TA0CCR1 = 10;

/* TA0CCR2, Timer_A Capture/Compare Register 2 */

TA0CCR2 = 10;

/*

* TA0CTL, Timer_A3 Control Register

*

* TASSEL_2 -- SMCLK

* ID_0 -- Divider - /1

* MC_1 -- Up Mode

*/

TA0CTL = TASSEL_2 | ID_0 | MC_1;

Loading...

Loading...