115

TMS570LS0714

www.ti.com

SPNS226E –JUNE 2013–REVISED NOVEMBER 2016

Submit Documentation Feedback

Product Folder Links: TMS570LS0714

Peripheral Information and Electrical SpecificationsCopyright © 2013–2016, Texas Instruments Incorporated

(1) For V

CCAD

and V

SSAD

recommended operating conditions, see Section 5.4.

(2) Input currents into any ADC input channel outside the specified limits could affect conversion results of other channels.

7.5.3 ADC Electrical and Timing Specifications

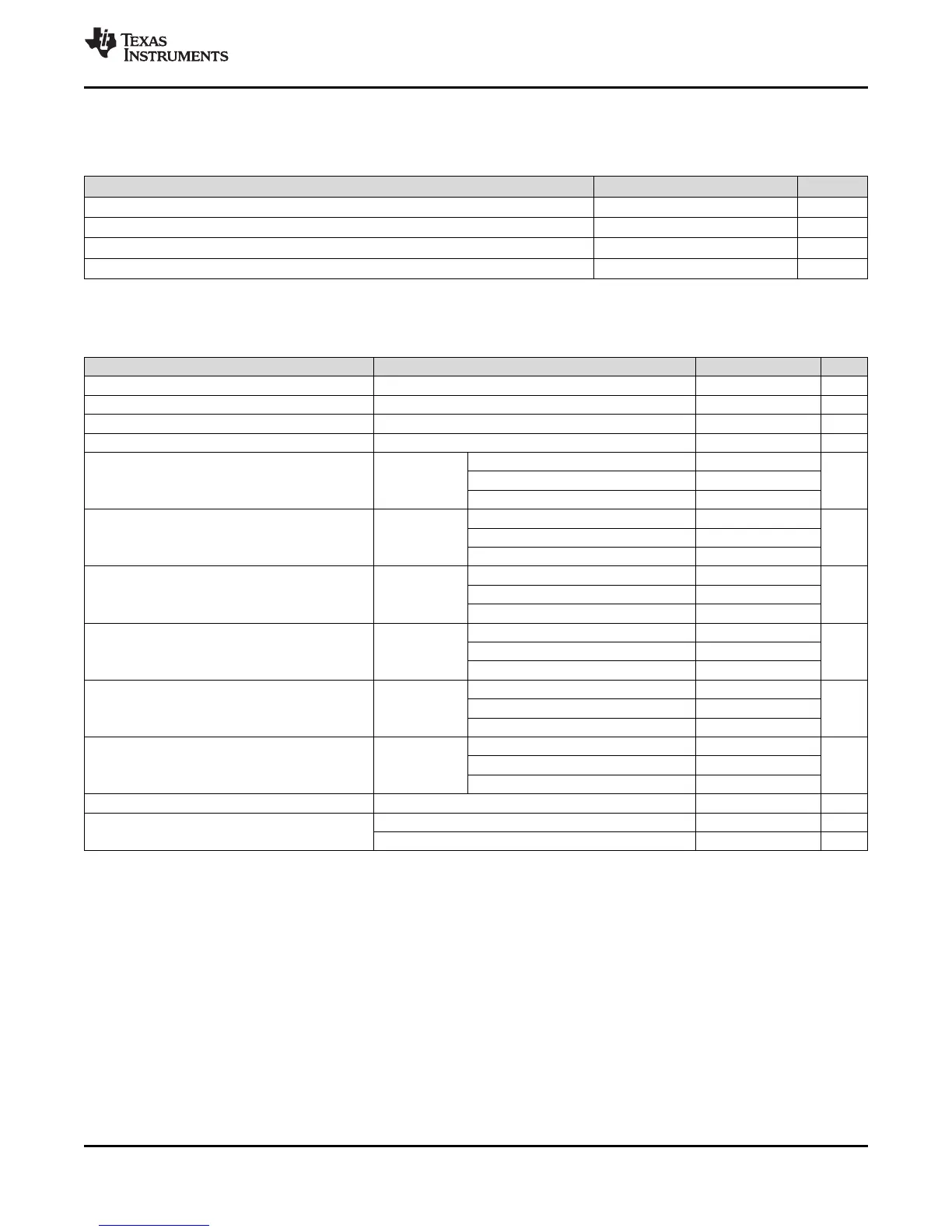

Table 7-23. MibADC Recommended Operating Conditions

PARAMETER MIN MAX UNIT

AD

REFHI

A-to-D high-voltage reference source AD

REFLO

V

CCAD

(1)

V

AD

REFLO

A-to-D low-voltage reference source V

SSAD

(1)

AD

REFHI

V

V

AI

Analog input voltage AD

REFLO

AD

REFHI

V

I

AIC

Analog input clamp current

(2)

(VAI < VSSAD – 0.3 or VAI > VCCAD + 0.3) –2 2 mA

(1) If a shared channel is being converted by both ADC converters at the same time, the on-state leakage is equal to I

AOSB1

+ I

AOSB2

.

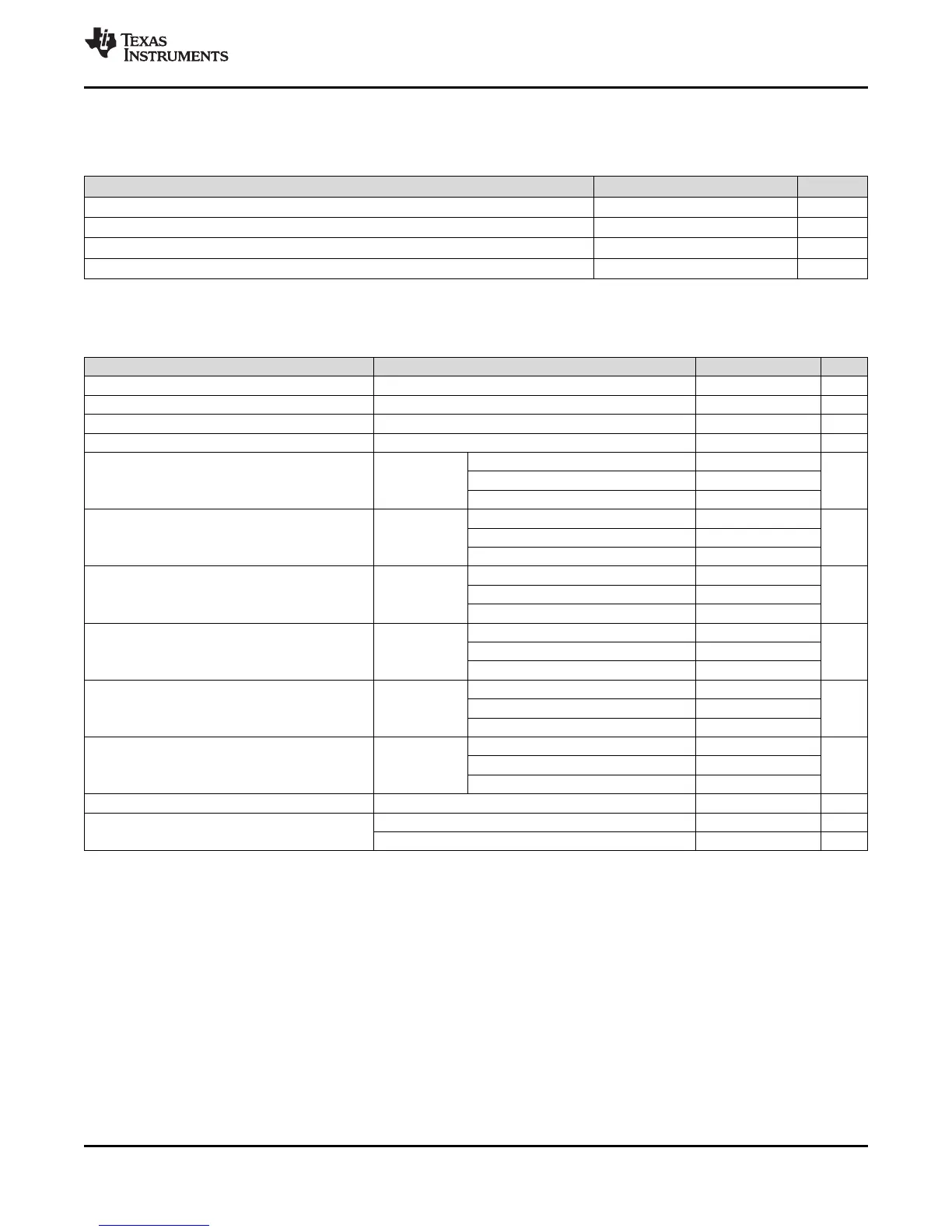

Table 7-24. MibADC Electrical Characteristics Over Full Ranges of Recommended Operating Conditions

PARAMETER DESCRIPTION/CONDITIONS MIN MAX UNIT

R

mux

Analog input mux on-resistance See Figure 7-12 250 Ω

R

samp

ADC sample switch on-resistance See Figure 7-12 250 Ω

C

mux

Input mux capacitance See Figure 7-12 16 pF

C

samp

ADC sample capacitance See Figure 7-12 13 pF

I

AIL

Analog off-state input leakage current

V

CCAD

= 3.6 V

maximum

V

SSAD

≤ V

IN

< V

SSAD

+ 100 mV –300 200

nAV

SSAD

+ 100 mV ≤ V

IN

≤ V

CCAD

– 200 mV –200 200

V

CCAD

– 200 mV < V

IN

≤ V

CCAD

–200 500

I

AIL

Analog off-state input leakage current

V

CCAD

= 5.25 V

maximum

V

SSAD

≤ V

IN

< V

SSAD

+ 300 mV –1000 250

nAV

SSAD

+ 300 mV ≤ V

IN

≤ V

CCAD

– 300 mV –250 250

V

CCAD

– 300 mV < V

IN

≤ V

CCAD

–250 1000

I

AOSB1

(1)

ADC1 Analog on-state input bias current

V

CCAD

= 3.6 V

maximum

V

SSAD

≤ V

IN

< V

SSAD

+ 100 mV –8 2

µAV

SSAD

+ 100 mV < V

IN

< V

CCAD

– 200 mV –4 2

V

CCAD

– 200 mV < V

IN

< V

CCAD

–4 12

I

AOSB2

(1)

ADC2 Analog on-state input bias current

V

CCAD

= 3.6 V

maximum

V

SSAD

≤ V

IN

< V

SSAD

+ 100 mV –7 2

µAV

SSAD

+ 100 mV ≤ V

IN

≤ V

CCAD

– 200 mV –4 2

V

CCAD

- 200 mV < V

IN

≤ V

CCAD

–4 10

I

AOSB1

(1)

ADC1 Analog on-state input bias current

V

CCAD

= 5.25 V

maximum

V

SSAD

≤ V

IN

< V

SSAD

+ 300 mV –10 3

µAV

SSAD

+ 300 mV ≤ V

IN

≤ V

CCAD

– 300 mV –5 3

V

CCAD

– 300 mV < V

IN

≤ V

CCAD

–5 14

I

AOSB2

(1)

ADC2 Analog on-state input bias current

V

CCAD

= 5.25 V

maximum

V

SSAD

≤ V

IN

< V

SSAD

+ 300 mV –8 3

µAV

SSAD

+ 300 mV ≤ V

IN

≤ V

CCAD

– 300 mV –5 3

V

CCAD

– 300 mV < V

IN

≤ V

CCAD

–5 12

I

ADREFHI

AD

REFHI

input current AD

REFHI

= V

CCAD

, AD

REFLO

= V

SSAD

3 mA

I

CCAD

Static supply current

Normal operating mode 15 mA

ADC core in power down mode 5 µA

Loading...

Loading...