25

TMS570LS0714

www.ti.com

SPNS226E –JUNE 2013–REVISED NOVEMBER 2016

Submit Documentation Feedback

Product Folder Links: TMS570LS0714

Terminal Configuration and FunctionsCopyright © 2013–2016, Texas Instruments Incorporated

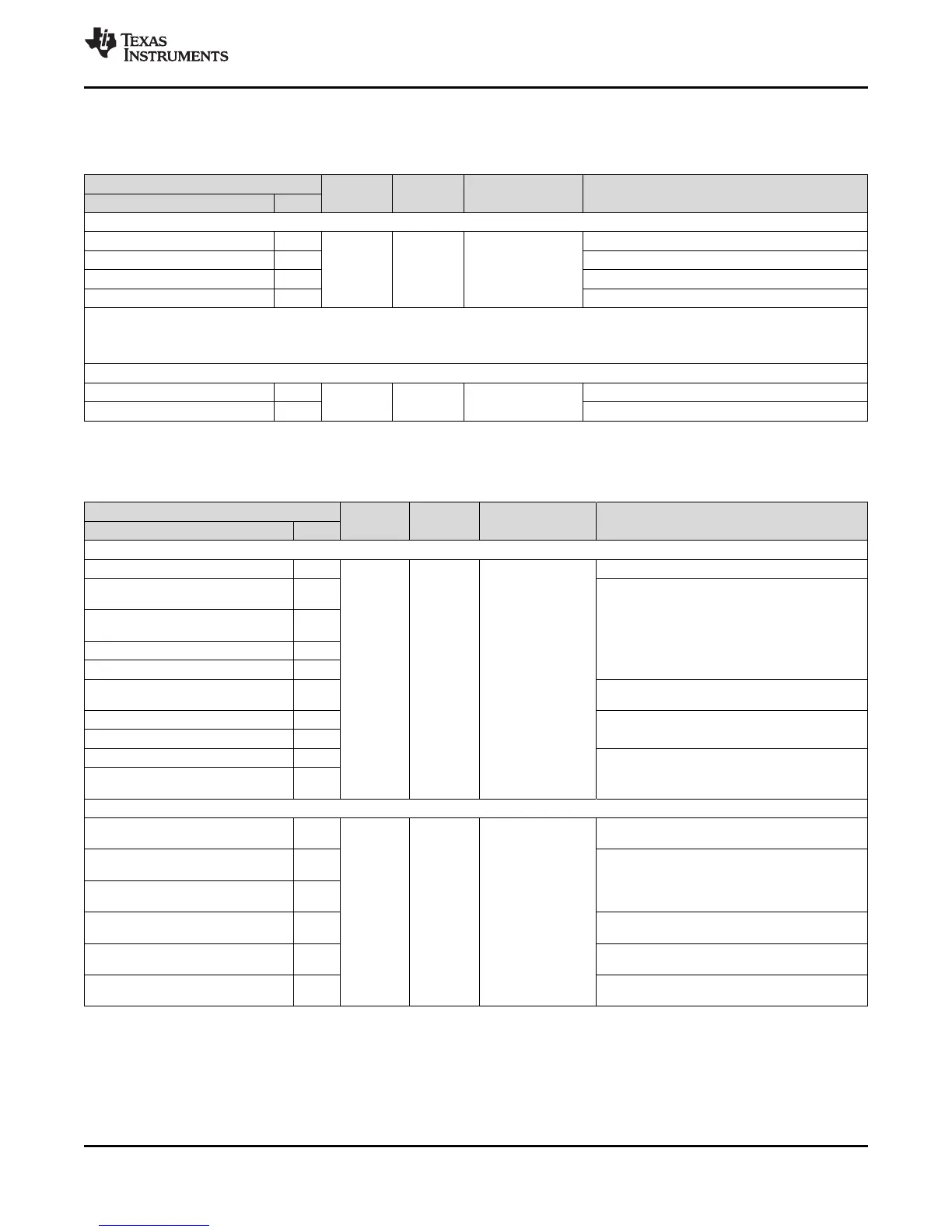

4.2.2.7 Standard Serial Peripheral Interfaces (SPI2 and SPI4)

Table 4-26. PZ Standard Serial Peripheral Interfaces (SPI2 and SPI4)

Terminal Signal Type Reset Pull

State

Pull Type Description

Signal Name 100 PZ

SPI2

SPI2CLK 71 I/O Pullup Programmable, 20 µA SPI2 Serial Clock, or GPIO

SPI2nCS[0] 23 SPI2 Chip Select, or GPIO

SPI2SIMO 70 SPI2 Slave-In-Master-Out, or GPIO

SPI2SOMI 69 SPI2 Slave-Out-Master-In, or GPIO

The drive strengths for the SPI2CLK, SPI2SIMO and SPI2SOMI signals are selected individually by configuring the respective SRS bits of the SPIPC9 register

fo SPI2.

SRS = 0 for 8mA drive (fast). This is the default mode as the SRS bits in the SPIPC9 register default to 0.

SRS = 1 for 2mA drive (slow)

SPI4

N2HET1[0] / SPI4CLK / EPWM2B 19 I/O Pulldown Programmable, 20 µA SPI2 Serial Clock, or GPIO

N2HET1[2] / SPI4SIMO / EPWM3A 22 SPI2 Slave-In-Master-Out, or GPIO

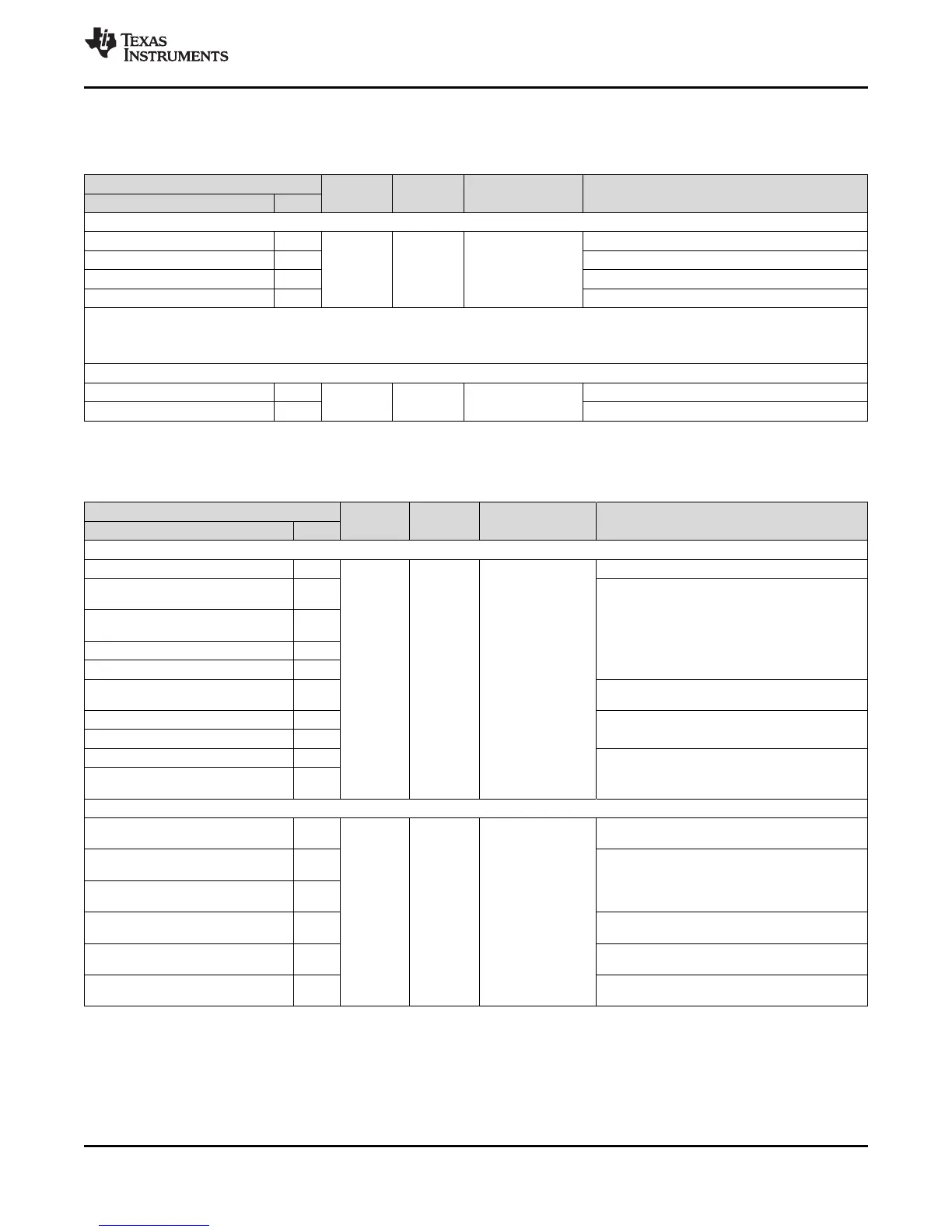

4.2.2.8 Multibuffered Serial Peripheral Interface (MibSPI1 and MibSPI3)

Table 4-27. PZ Multibuffered Serial Peripheral Interface (MibSPI1 and MibSPI3)

Terminal Signal

Type

Reset Pull

State

Pull Type Description

Signal Name 100 PZ

MibSPI1

MIBSPI1CLK 67 I/O Pullup Programmable, 20 µA MibSPI1 Serial Clock, or GPIO

MIBSPI1nCS[0]/MIBSPI1SOMI[1]/

ECAP6

73 MibSPI1 Chip Select, or GPIO

MIBSPI1nCS[1]/N2HET1[17]/

EQEP1S

93

MIBSPI1nCS[2]/N2HET1[19] 27

MIBSPI1nCS[3]/N2HET1[21] 39

MIBSPI1nENA/N2HET1[23]/

ECAP4

68 MibSPI1 Enable, or GPIO

MIBSPI1SIMO[0] 65 MibSPI1 Slave-In-Master-Out, or GPIO

N2HET1[8]/MIBSPI1SIMO[1] 74

MIBSPI1SOMI[0] 66 MibSPI1 Slave-Out-Master-In, or GPIO

MIBSPI1nCS[0]/MIBSPI1SOMI[1]/

ECAP6

73

MibSPI3

MIBSPI3CLK/AWM1_EXT_SEL[1]/

EQEP1A

36 I/O Pullup Programmable, 20 µA MibSPI3 Serial Clock, or GPIO

MIBSPI3nCS[0]/AD2EVT/GIOB[2]/

EQEP1I/N2HET2_PIN_nDIS

38 MibSPI3 Chip Select, or GPIO

MIBSPI3nENA/MIBSPI3nCS[5]/

N2HET1[31]/EQEP1B

37

MIBSPI3nENA/MIBSPI3nCS[5]/

N2HET1[31]/EQEP1B

37 MibSPI3 Enable, or GPIO

MIBSPI3SIMO[0]/AWM1_EXT_SEL[0]/

ECAP3

35 MibSPI3 Slave-In-Master-Out, or GPIO

MIBSPI3SOMI[0]/AWM1_EXT_ENA/

ECAP2

34 MibSPI3 Slave-Out-Master-In, or GPIO

Loading...

Loading...