62

TMS570LS0714

SPNS226E –JUNE 2013–REVISED NOVEMBER 2016

www.ti.com

Submit Documentation Feedback

Product Folder Links: TMS570LS0714

System Information and Electrical Specifications Copyright © 2013–2016, Texas Instruments Incorporated

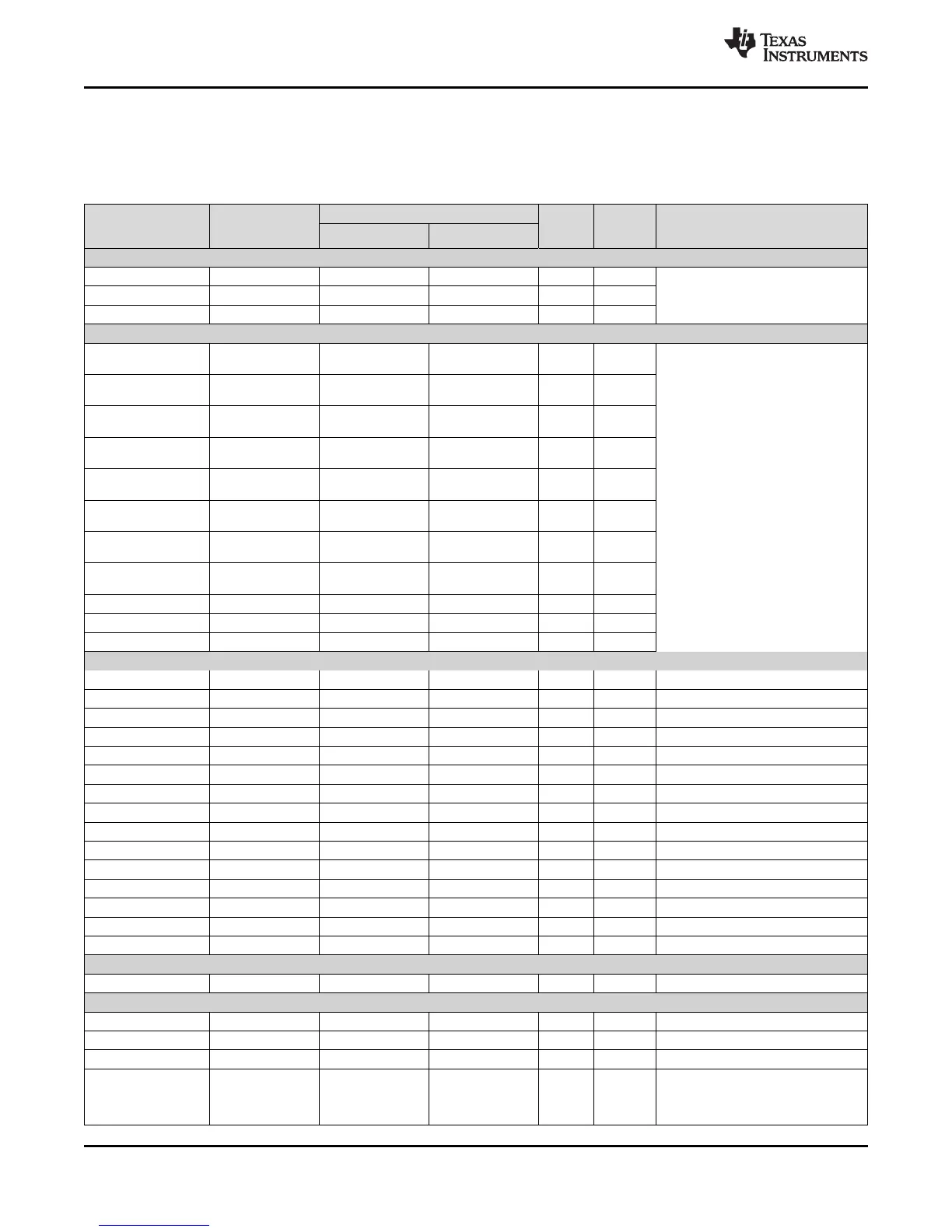

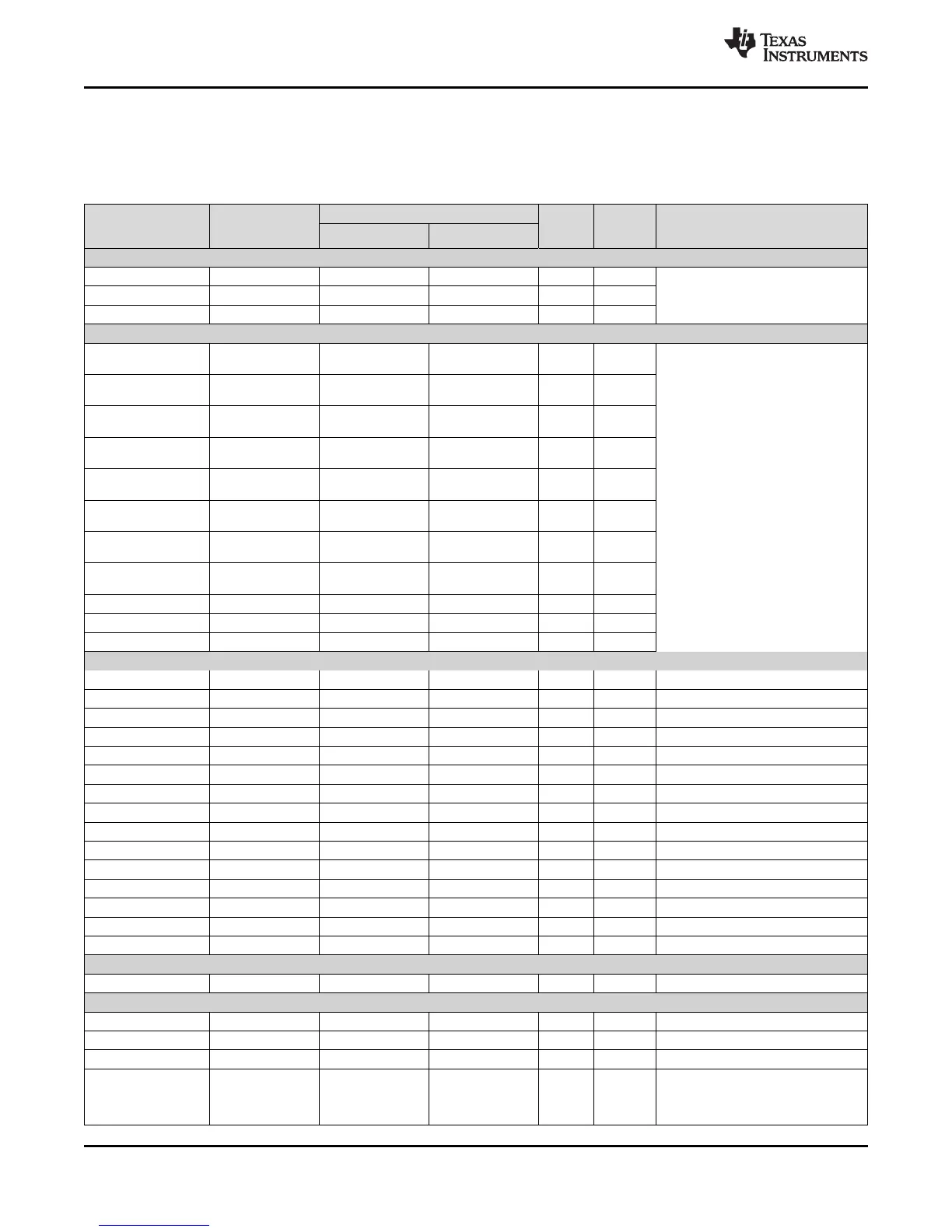

6.9.2 Memory Map Table

See Figure 1-1 for block diagrams showing the devices interconnect.

Table 6-20. Device Memory Map

MODULE NAME

FRAME CHIP

SELECT

FRAME ADDRESS RANGE

FRAME

SIZE

ACTUAL

SIZE

RESPONSE FOR ACCESS TO

UNIMPLEMENTED LOCATIONS IN

FRAME

START END

Memories tightly coupled to the ARM Cortex-R4F CPU

TCM Flash CS0 0x0000_0000 0x00FF_FFFF 16MB 768KB

AbortTCM RAM + RAM ECC CSRAM0 0x0800_0000 0x0BFF_FFFF 64MB 96KB

Mirrored Flash Flash mirror frame 0x2000_0000 0x20FF_FFFF 16MB 768KB

Flash Module Bus2 Interface

Customer OTP, TCM

Flash Banks

0xF000_0000 0xF000_1FFF 8KB 4KB

Abort

Customer OTP,

Bank 7

0xF000_E000 0xF000_FFFF 8KB 1KB

Customer OTP–ECC,

TCM Flash Banks

0xF004_0000 0xF004_03FF 1KB 512B

Customer OTP–ECC,

Bank 7

0xF004_1C00 0xF004_1FFF 1KB 128B

TI OTP, TCM Flash

Banks

0xF008_0000 0xF008_1FFF 8KB 4KB

TI OTP,

Bank 7

0xF008_E000 0xF008_FFFF 8KB 1KB

TI OTP–ECC, TCM

Flash Banks

0xF00C_0000 0xF00C_03FF 1KB 512B

TI OTP–ECC,

Bank 7

0xF00C_1C00 0xF00C_1FFF 1KB 128B

Bank 7 – ECC 0xF010_0000 0xF013_FFFF 256KB 8KB

Bank 7 0xF020_0000 0xF03F_FFFF 2MB 64KB

Flash Data Space ECC 0xF040_0000 0xF04F_FFFF 1MB 128KB

SCR5: Enhanced Timer Peripherals

ePWM1 0xFCF7_8C00 0xFCF7_8CFF 256B 256B Abort

ePWM2 0xFCF7_8D00 0xFCF7_8DFF 256B 256B Abort

ePWM3 0xFCF7_8E00 0xFCF7_8EFF 256B 256B Abort

ePWM4 0xFCF7_8F00 0xFCF7_8FFF 256B 256B Abort

ePWM5 0xFCF7_9000 0xFCF7_90FF 256B 256B Abort

ePWM6 0xFCF7_9100 0xFCF7_91FF 256B 256B Abort

ePWM7 0xFCF7_9200 0xFCF7_92FF 256B 256B Abort

eCAP1 0xFCF7_9300 0xFCF7_93FF 256B 256B Abort

eCAP2 0xFCF7_9400 0xFCF7_94FF 256B 256B Abort

eCAP3 0xFCF7_9500 0xFCF7_95FF 256B 256B Abort

eCAP4 0xFCF7_9600 0xFCF7_96FF 256B 256B Abort

eCAP5 0xFCF7_9700 0xFCF7_97FF 256B 256B Abort

eCAP6 0xFCF7_9800 0xFCF7_98FF 256B 256B Abort

eQEP1 0xFCF7_9900 0xFCF7_99FF 256B 256B Abort

eQEP2 0xFCF7_9A00 0xFCF7_9AFF 256B 256B Abort

Cyclic Redundancy Checker (CRC) Module Registers

CRC CRC frame 0xFE00_0000 0xFEFF_FFFF 16MB 512B Accesses above 0x200 generate abort.

Peripheral Memories

MIBSPI5 RAM PCS[5] 0xFF0A_0000 0xFF0B_FFFF 128KB 2KB Abort for accesses above 2KB

MIBSPI3 RAM PCS[6] 0xFF0C_0000 0xFF0D_FFFF 128KB 2KB Abort for accesses above 2KB

MIBSPI1 RAM PCS[7] 0xFF0E_0000 0xFF0F_FFFF 128KB 2KB Abort for accesses above 2KB

DCAN3 RAM PCS[13] 0xFF1A_0000 0xFF1B_FFFF 128KB 2KB

Wrap around for accesses to

unimplemented address offsets lower

than 0x7FF. Abort generated for

accesses beyond offset 0x800.

Loading...

Loading...