7 Series FPGAs GTP Transceivers User Guide www.xilinx.com 211

UG482 (v1.9) December 19, 2016

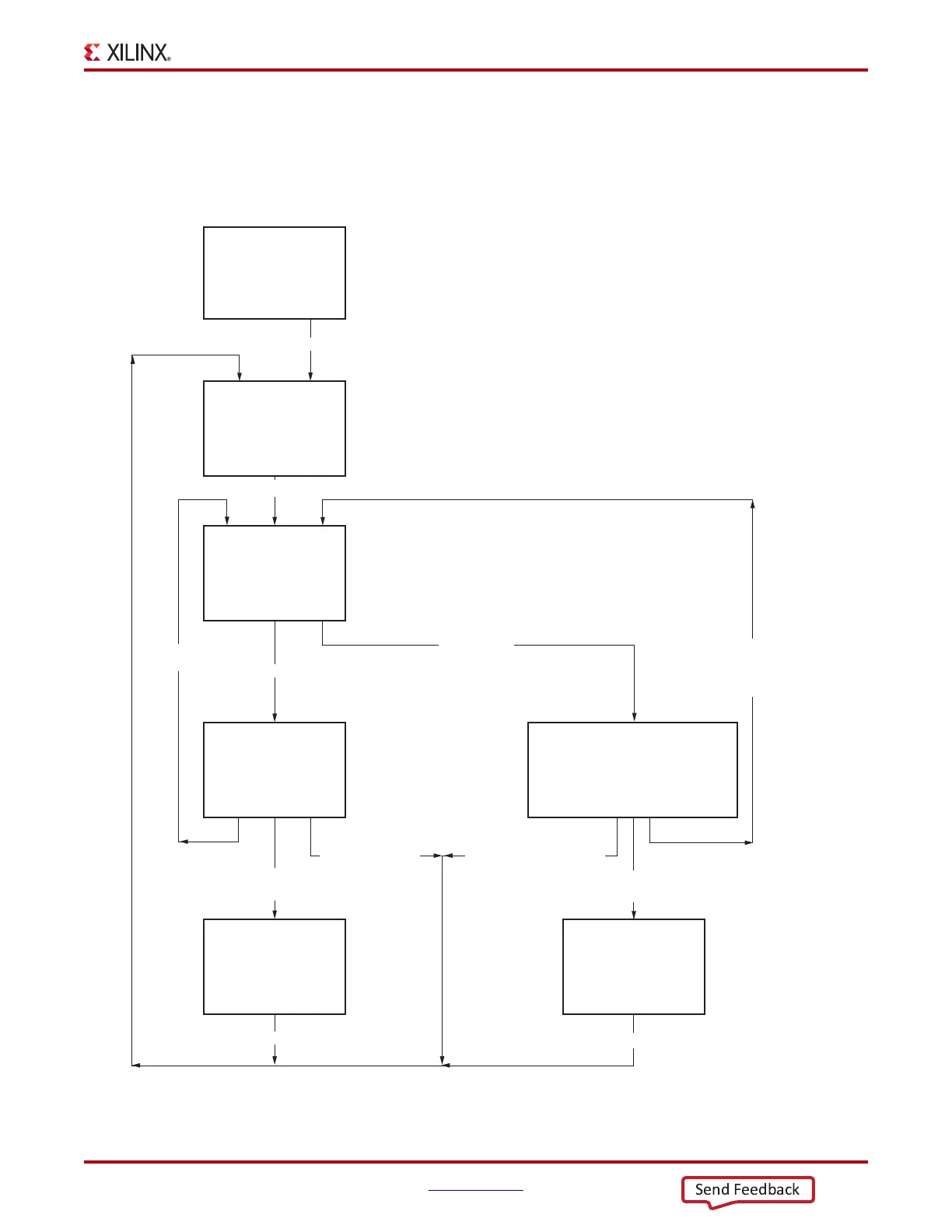

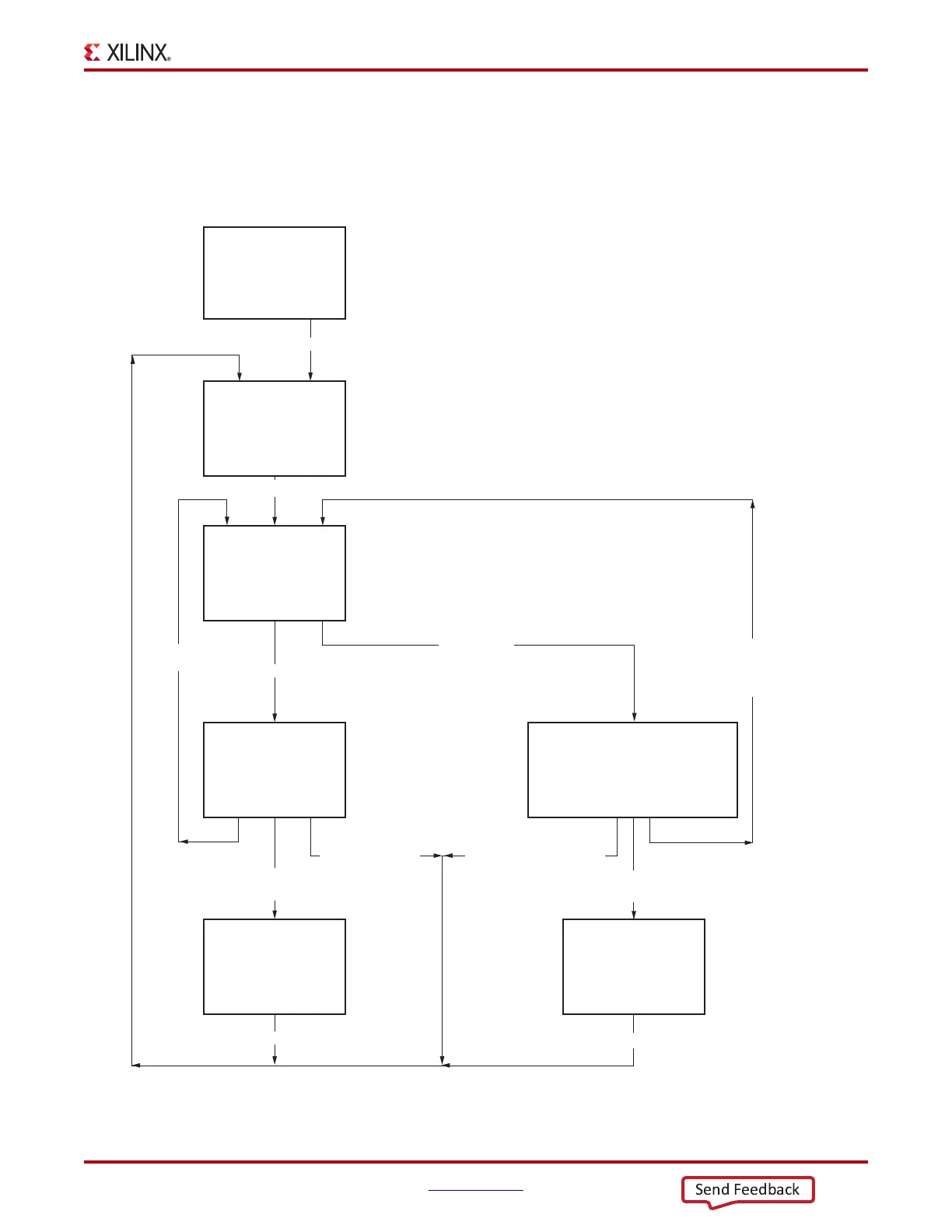

RX Gearbox

synchronization state machine to the RX gearbox and tells it to slip the data alignment. This process

of slipping and testing the synchronization header repeats until block lock is achieved. When using

the RX gearbox, a block synchronization state machine is required in the FPGA logic. Figure 4-57

shows the operation of a block synchronization state machine. The 7 Series FPGAs Transceivers

Wizard has example code for this type of module.

X-Ref Target - Figure 4-57

Figure 4-57: Block Synchronization State Machine

LOCK_INIT

block_lock <= false

test_sh <= false

RESET_CNT

sh_cnt <= 0

sh_invalid_cnt <= 0

slip_done <= false

TEST_SH

test_sh <= false

VALID_SH

sh_cnt <= sh_cnt + 1

64_GOOD

block_lock <= true

SLIP

block_lock <= false

SLIP <= true

INVALID_SH

sh_cnt <= sh_cnt + 1

sh_invalid_cnt <= sh_invalid_cnt + 1

sh_cnt = 64 AND

sh_invalid_cnt = 0

sh_cnt = 64 AND

sh_invalid_cnt > 0

sh_cnt = 64 AND

sh_invalid_cnt < 16 AND

block_lock = true

sh_invalid_cnt = 16 OR

block_lock = false

slip_done = true

sh_valid = 0

Unconditional Transition

sh_valid = 1

test_sh = true AND

sh_cnt < 64

test_sh = 1

Unconditional Transition

test_sh = true AND

sh_cnt < 64 AND

sh_invalid_cnt < 16 AND

block_lock = true

UG482_c4_39_111011

Loading...

Loading...