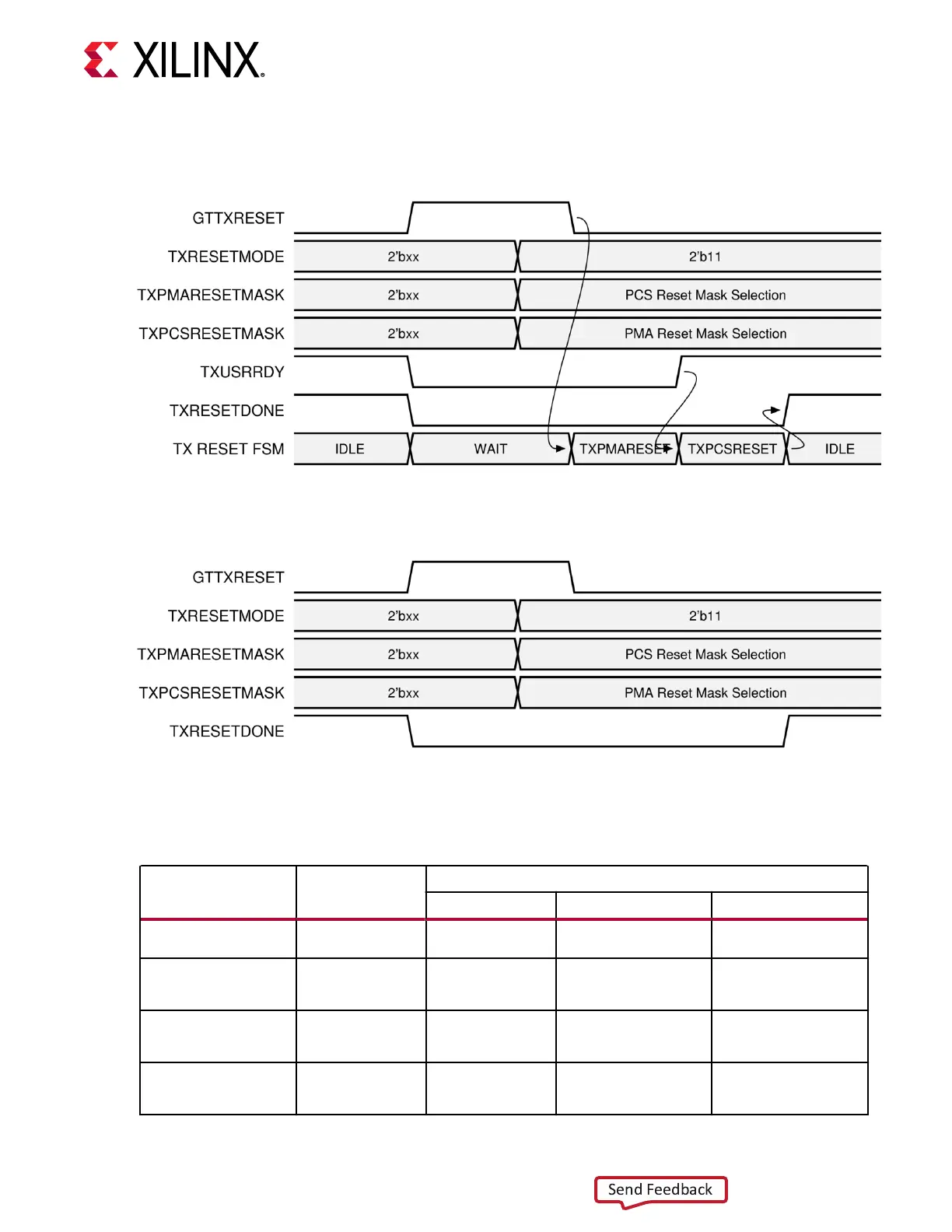

Figure 16: GTM Transmitter Reset after GTTXRESET Pulse in Component Sequential

Mode

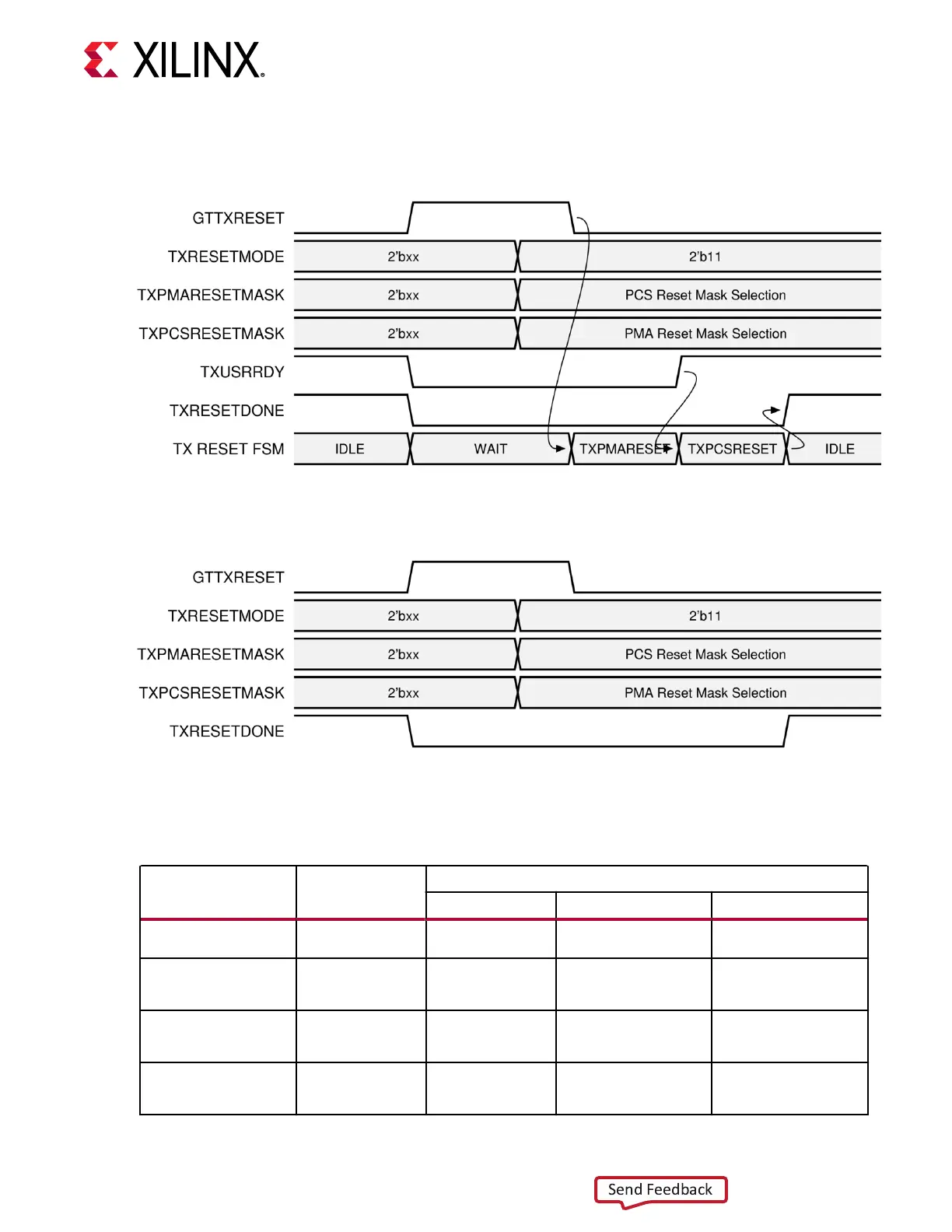

Figure 17: GTM Transmitter Reset after GTTXRESET Pulse in Component Single Mode

The following table lists the recommended resets for common situaons.

Table 16: Recommended Transmitter Resets for Common Situations

Situation

Components to

be Reset

Recommended TX Reset Setting

TXRESETMODE TXPMARESETMASK TXPCSRESETMASK

1

After power up and

configuration

PLL, Entire TX

2'b00 2’b11 2’b11

After turning on a

reference clock to the

PLL being used

PLL, Entire TX

2'b00 2’b11 2’b11

After changing the

reference clock to the

PLL being used

PLL, Entire TX

2'b00 2’b11 2’b11

After assertion/

deassertion of PLLPD for

the PLL being used

PLL, Entire TX

2'b00 2’b11 2’b11

Chapter 2: Shared Features

UG581 (v1.0) January 4, 2019 www.xilinx.com

Virtex UltraScale+ GTM Transceivers 32

Loading...

Loading...