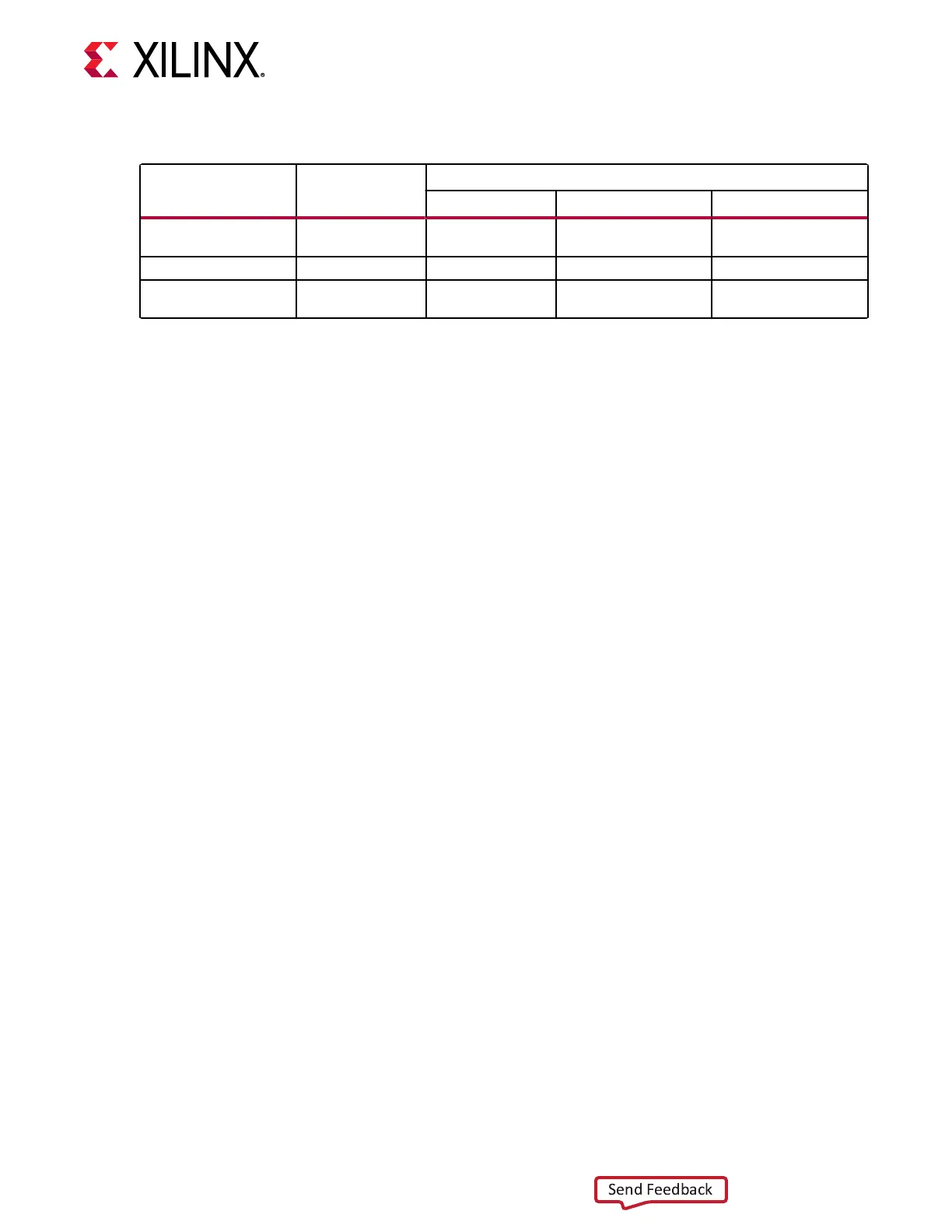

Table 16: Recommended Transmitter Resets for Common Situations (cont'd)

Situation

Components to

be Reset

Recommended TX Reset Setting

TXRESETMODE TXPMARESETMASK TXPCSRESETMASK

1

After assertion/

deassertion of TXPD

Entire TX

2'b00 2’b11 2’b11

TX rate change TX PMA and TX PCS

2'b00 2’b11 2’b11

TX parallel clock source

reset

TX PCS 2'b00/2'b11

2’b00 2’b11

Notes:

1. TXPCSRESETMASK[0] can be set to 0 if the FEC is bypassed.

After Power-up and Configuration

The PLL being used and the enre GTM TX require a reset aer conguraon. See GTM

Transceiver TX Reset in Response to Compleon of Conguraon.

After Turning on a Reference Clock to the LCPLL/

RPLL Being Used

If the reference clock(s) changes or the GTM transceiver(s) are powered up aer conguraon,

perform a full TX sequenal reset aer the PLL fully completes its reset procedure.

After Changing the Reference Clock to the PLL being

Used

Whenever the reference clock input to the PLL is changed, the PLL must be reset aerwards to

ensure that it locks to the new frequency. Perform a full TX sequenal reset aer the PLL fully

completes its reset procedure.

After Assertion/Deassertion of PLLPD for the PLL

being Used

When the PLL being used goes back to normal operaon aer power down, the PLL must be

reset. Perform a full TX sequenal reset aer the PLL fully completes its reset procedure.

After Assertion/Deassertion of TXPD[1:0]

Aer the TXPD signal is deasserted, perform a full TX sequenal reset.

Chapter 2: Shared Features

UG581 (v1.0) January 4, 2019 www.xilinx.com

Virtex UltraScale+ GTM Transceivers 33

Loading...

Loading...