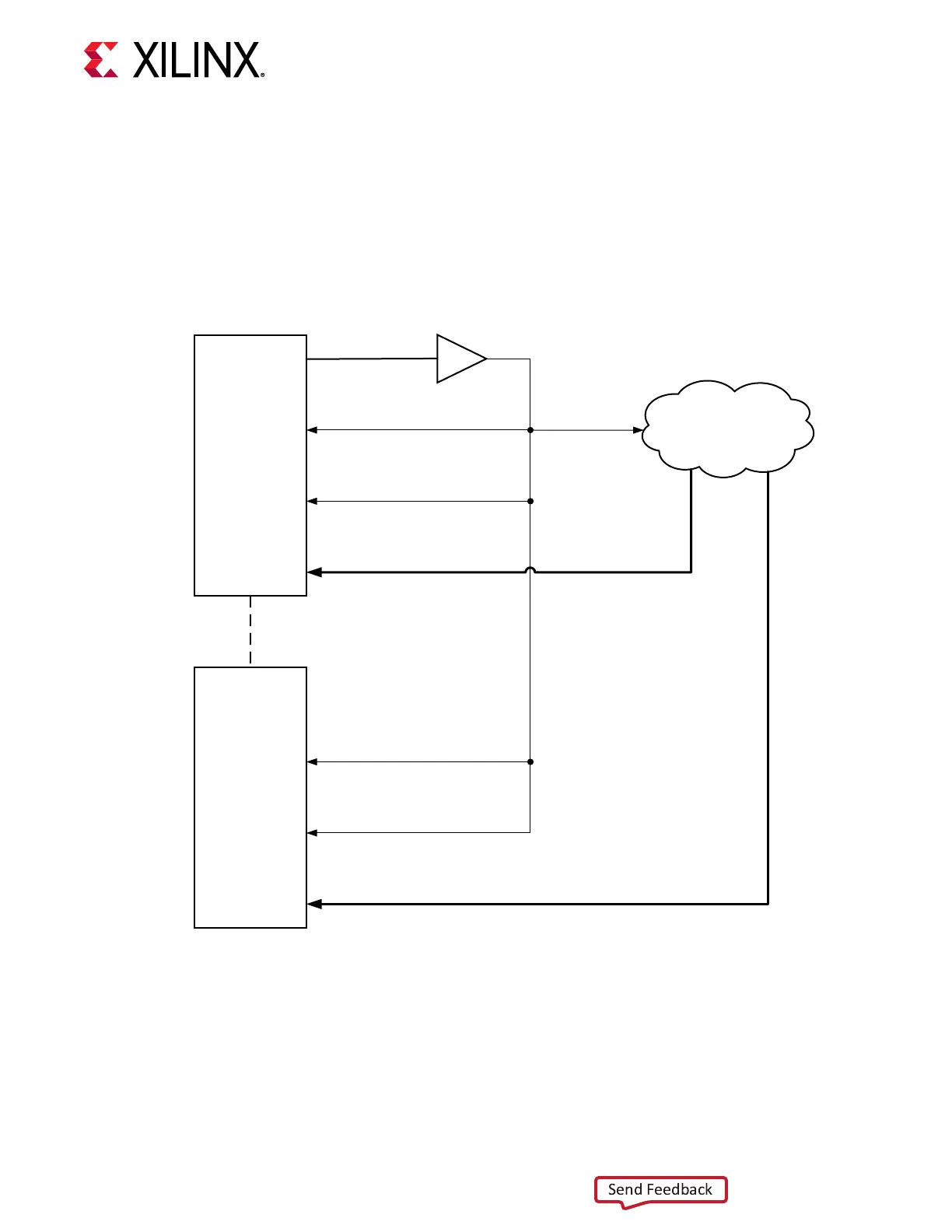

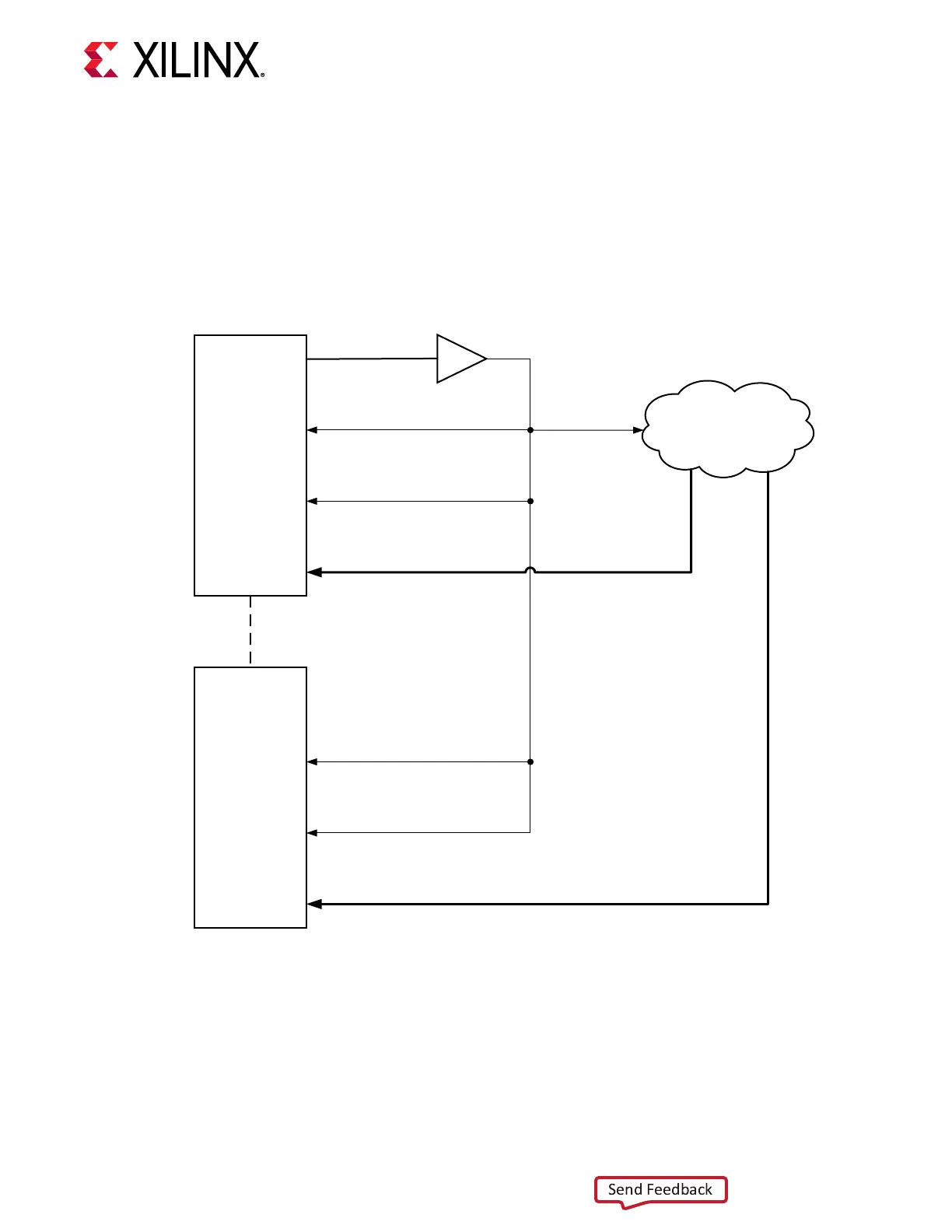

Similarly, the following gure shows the same sengs in a mulple-lane conguraon. In a mul-

lane conguraon, the middle-most GTM transceiver should be selected to be the source of

TXPROGDIVCLK. For example, in a mul-lane conguraon of six GTM transceivers consisng

of three conguous Duals, one of the middle GTM transceivers in the middle Dual should be

selected as the source of TXPROGDIVCLK.

Figure 27: Multiple Lanes—TXPROGDIVCLK Drives TXUSRCLK and TXUSRCLK2 (64-Bit,

80-Bit, or 128-Bit Mode)

Design in UltraScale

Architecture

UltraScale

Devices GTM

Transceiver

TXPROGDIVCLK

BUFG_GT

1

TXUSRCLK2

2

TXUSRCLK

2,3

TXDATA (TX data width =

64/80/128 bits)

UltraScale

Devices GTM

Transceiver

TXDATA (TX data width = 64/80/128 bits)

TXUSRCLK

2,3

TXUSRCLK2

2

X20912-111918

Notes relevant to the gure:

1. For details about placement constraints and restricons on clocking resources (such as

BUFG_GT and BUFG_GT_SYNC), refer to the UltraScale Architecture Clocking Resources User

Guide (UG572).

2. F

TXUSRCLK2

= F

TXUSRCLK

.

Chapter 3: Transmitter

UG581 (v1.0) January 4, 2019 www.xilinx.com

Virtex UltraScale+ GTM Transceivers 60

Loading...

Loading...