3. TXUSRCLK can be ed to 1’b0 if GEN_TXUSRCLK = 1’b1.

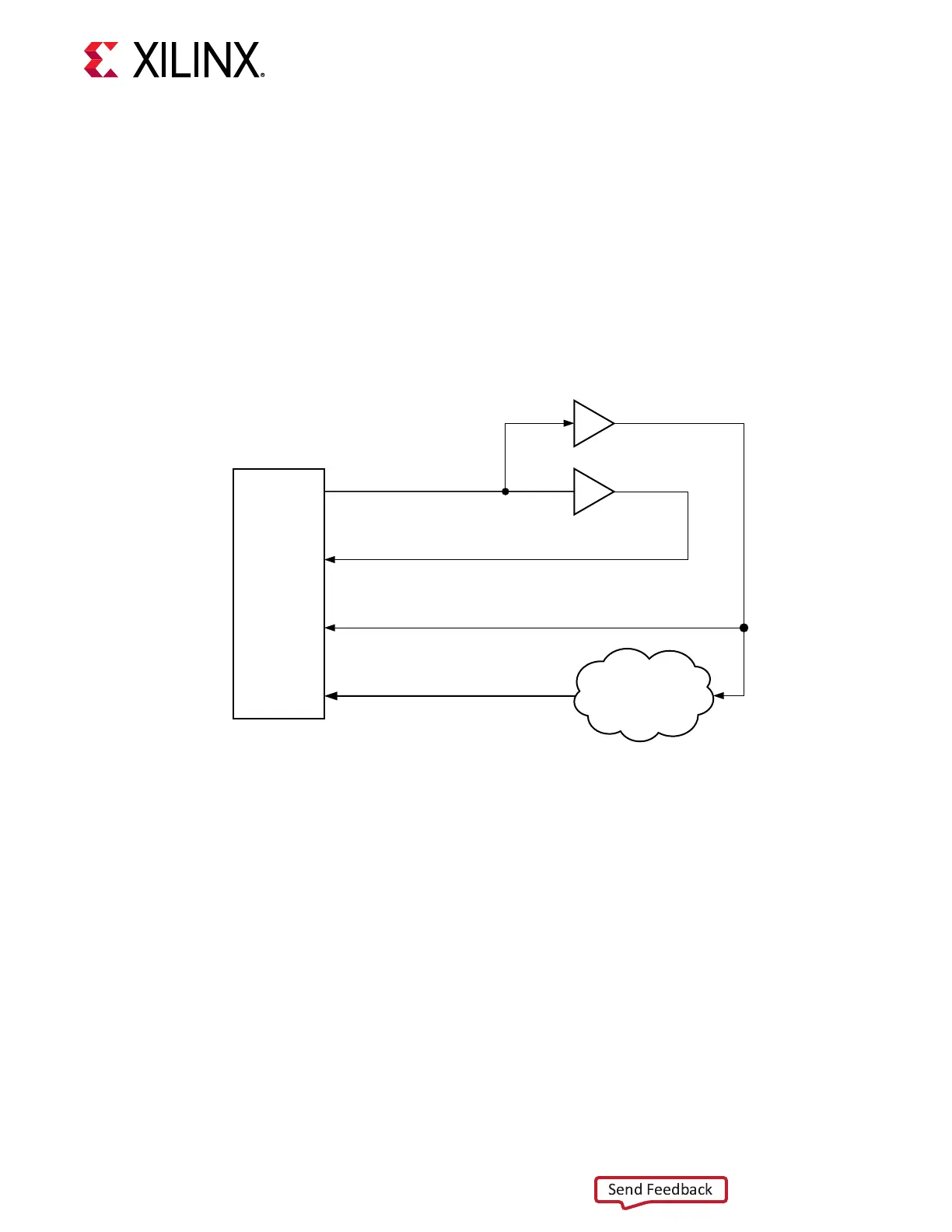

TXPROGDIVCLK Driving GTM Transceiver TX in 128-Bit, 160-Bit, or

256-Bit Mode

In the following gure, TXPROGDIVCLK is used to drive TXUSRCLK and TXUSRCLK2 in 128-bit,

160-bit, or 256-bit mode in a single-lane conguraon. In all cases, the frequency of

TXUSRCLK2 is equal to half of the TXUSRCLK frequency.

Figure 28: Single Lane—TXPROGDIVCLK Drives TXUSRCLK and TXUSRCLK2 (128-Bit,

160-Bit, or 256-Bit Mode)

Design in UltraScale

Architecture

÷1

UltraScale

Devices GTM

Transceiver

TXPROGDIVCLK

BUFG_GT

1

TXUSRCLK2

2

TXUSRCLK

2

TXDATA (TX data width = 128/160/256 bits)

÷2

BUFG_GT

1

X20913-111918

Notes relevant to the gure:

1. For details about placement constraints and restricons on clocking resources (such as

BUFG_GT and BUFG_GT_SYNC), refer to the UltraScale Architecture Clocking Resources User

Guide (UG572).

2. F

TXUSRCLK2

= F

TXUSRCLK

/2.

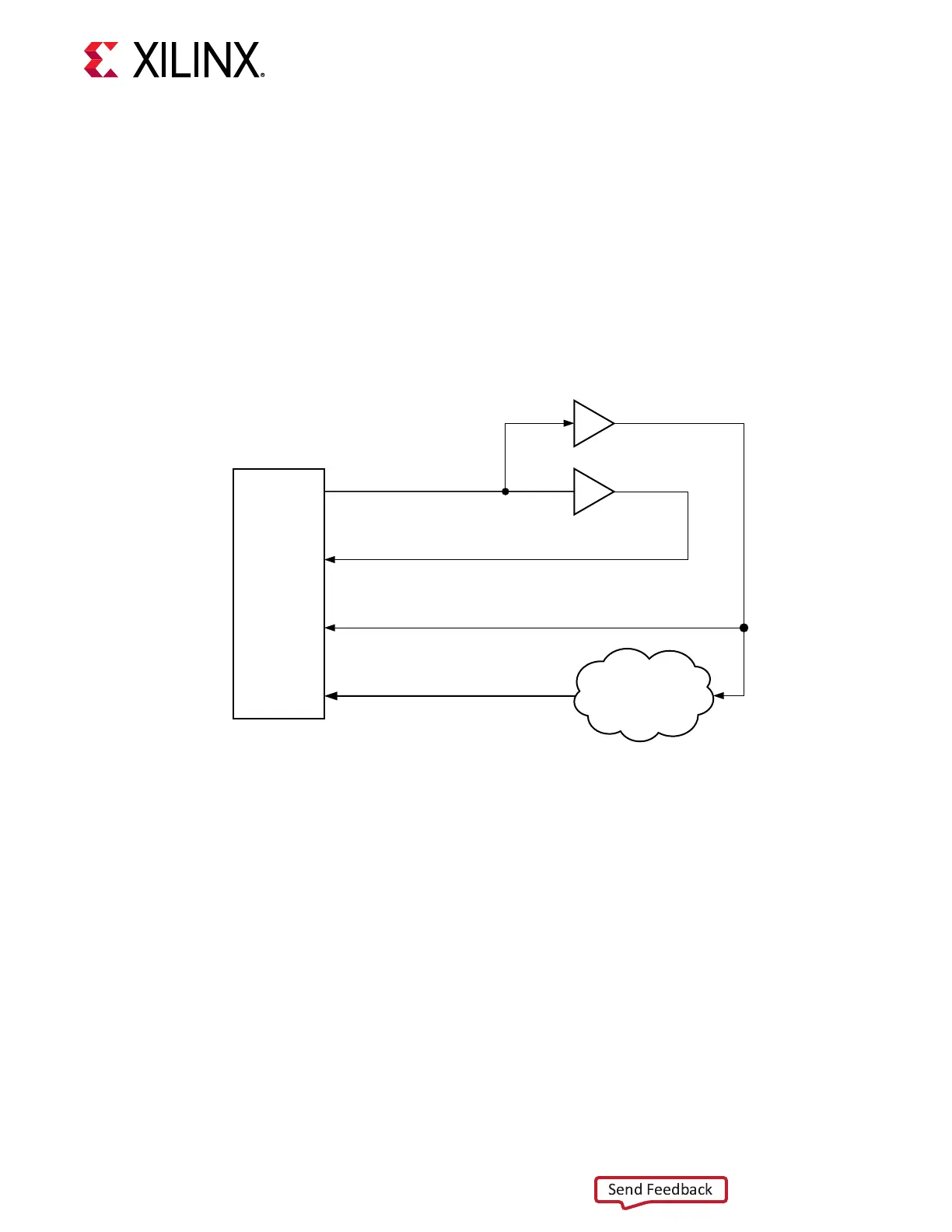

Similarly, the following gure shows the same sengs in a mulple-lane conguraon. In a mul-

lane conguraon, the middle-most GTM transceiver should be selected to be the source of

TXPROGDIVCLK. For example, in a mul-lane conguraon of six GTM transceivers consisng

of three conguous Duals, one of the middle GTM transceivers in the middle Dual should be

selected as the source of TXPROGDIVCLK.

Chapter 3: Transmitter

UG581 (v1.0) January 4, 2019 www.xilinx.com

Virtex UltraScale+ GTM Transceivers 61

Loading...

Loading...